Introducción

Los drones, los coches inteligentes y los auriculares para realidad virtual (AR/ VR) utilizan varios sensores de imagen, a menudo de diferente tipo, con el fin de capturar datos sobre su entorno operativo. Para suministrar los datos de las imágenes que necesita el sistema, cada sensor debe estar conectado al procesador de aplicación (application processor, AP) del sistema, cuyo diseño presenta algunos retos para los ingenieros de sistemas embebidos. En primer lugar, los AP disponen de un número finito de puertos de E/S para conectarse a los sensores, por lo que los puertos de E/S se deben asignar cuidadosamente con el objetivo de asegurar que todos los componentes discretos que precisen una conexión al AP cuenten con esta. En segundo lugar, los drones y los auriculares para AR/VR deben ser de pequeño tamaño y alimentarse con baterías, por lo que los componentes utilizados en estas aplicaciones deben ser lo más pequeños y con un consumo lo más eficiente que sea posible. Una solución a la falta de puertos de E/S del AP consiste en utilizar Canales Virtuales, tal como se definen en la especificación MIPI CSI-2 (Camera Serial Interface-2), que puede concentrar hasta 16 flujos de diferentes sensores en un solo flujo que a continuación se puede enviar al AP a través de un solo puerto de E/S. La plataforma de hardware escogida para implementar un Canal Virtual es la FPGA (field programmable gate array). Otras plataformas de hardware necesitan mucho tiempo de diseño y es posible que no ofrezcan el bajo consumo que exigen aplicaciones como drones o auriculares para AR/VR. Algunos señalan que las FPGA ocupan demasiado espacio y que su consumo es excesivo como plataforma viable para un Canal Virtual. Pero los avances en el diseño y la fabricación de semiconductores han permitido desarrollar una nueva generación de FPGA más pequeñas y con un consumo más eficiente.

Análisis de la situación

La creciente demanda de drones, coches inteligentes y auriculares para AR/VR por parte de los consumidores está impulsando un enorme crecimiento en el mercado de sensores. Según Semico Research, las aplicaciones de automoción (con un crecimiento medio interanual del 27%), drones (27%) y auriculares para AR/VR (166%) impulsarán la demanda de sensores y prevé que los fabricantes de equipamiento original (OEM) de semiconductores suministrarán más de 1.500 millones de sensores de imagen al año en 2022. Las aplicaciones antes citadas necesitan diversos sensores para capturar datos en el entorno operativo de la aplicación. Por ejemplo, un coche inteligente podría utilizar varios sensores de imagen de alta definición para las cámaras de visión trasera y del entorno, un sensor LIDAR para detección de objetos y un sensor de radar para controlar el ángulo muerto. Esta proliferación de los sensores representa un problema ya que todos estos sensores necesitan enviar datos al AP del coche y el AP dispone de un número finito de puertos de E/S. El mayor número de sensores también aumenta la densidad de las conexiones al AP en la placa del circuito del dispositivo, ocupando así más espacio y dificultando el diseño de dispositivos más pequeños, como los auriculares. Una solución a la falta de puertos de E/S del AP consiste en utilizar Canales Virtuales. Los Canales Virtuales concentran los flujos de vídeo de diferentes sensores en un solo flujo que a continuación se puede enviar al AP a través de un solo puerto de E/S. Un estándar actual bien conocido para conectar sensores de cámaras a un AP es la especificación MIPI CSI-2 (Camera Serial Interface-2) desarrollada por la MIPI Alliance. CSI- 2 puede combinar hasta 16 flujos de datos diferentes en uno mediante la función Canal Virtual de CSI-2. No obstante, combinar los flujos de diferentes sensores de imagen en un solo flujo de vídeo supone algunos retos.

Retos de los canales virtuales

Combinar datos de sensores del mismo tipo en un solo canal no resulta complicado. Los sensores se pueden sincronizar y sus flujos de datos se pueden concatenar de forma que se puedan enviar al AP como una imagen con el doble de anchura. El reto surge de la necesidad de combinar los flujos de datos de diferentes sensores. Por ejemplo, un podría utilizar un sensor de imagen de alta resolución para detección de objetos con luz diurna y un sensor de IR de menor resolución con el fin de capturar patrones térmicos para detección de objetos por la noche. Estos sensores tienen diferentes frecuencias de imagen, resoluciones y anchos de banda que no se pueden sincronizar. Para seguir los diferentes flujos de vídeo, cada paquete de datos de CSI-2 se ha de marcar con un identificador de Canal Virtual de forma que el AP pueda procesar cada paquete dependiendo de las necesidades. Además de marcar los paquetes, la combinación de flujos de datos de diferentes tipos de sensores también exige sincronizar la carga útil de los datos de cada sensor. Si los sensores trabajan con diferentes velocidades de reloj se deben mantener separados los dominios del reloj para cada sensor. Estos dominios se sincronizan antes de su introducción en el AP.

Los canales virtuales necesitan un puente especial de hardware para procesamiento

La implementación de un puente para Canales Virtuales en hardware puede resolver las cuestiones descritas antes. Un puente especial para Canal Virtual permite conectar todos los sensores de imagen al puerto de E/S del puente con el fin de que este se pueda conectar al AP a través de un solo puerto, dejando así los valiosos puertos del AP a disposición de otros periféricos. Esto también resuelve la cuestión del espacio provocado por las múltiples conexiones entre los sensores y el AP en la placa del circuito; el puente concentra las pistas hasta el AP. Las FPGA permiten implementar rutas de datos en paralelo para cada entrada del sensor y que cada ruta tenga su propio dominio de reloj. Estos dominios se sincronizan en la etapa VC Merge (fusión de Canal Virtual) como muestra la siguiente figura, extrayendo así la carga de procesamiento del AP.

Ventajas del hardware de canal virtual basado en PLD

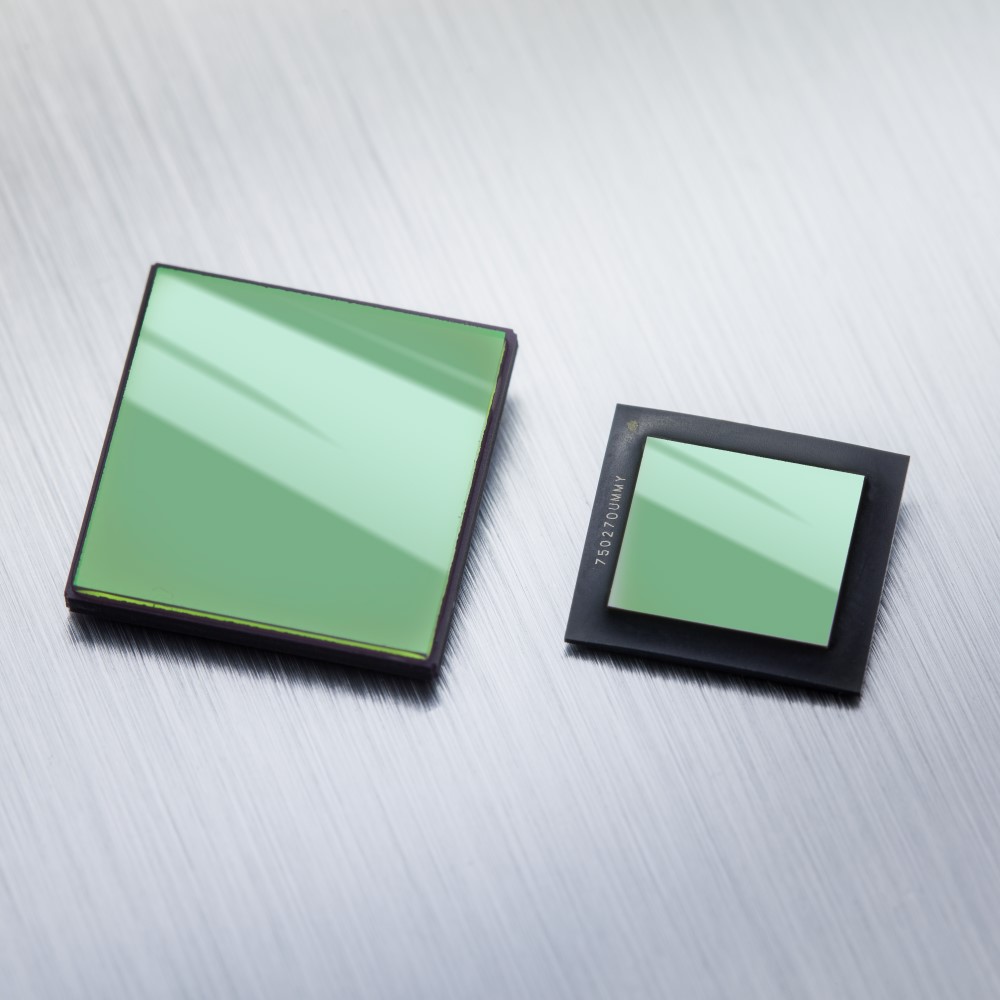

A la hora de implementar el soporte a un Canal Virtual en hardware, la plataforma más atractiva sobre un circuito integrado es la FPGA. Las FPGA son circuitos integrados con puertos de E/S flexibles, son compatibles con una amplia variedad de interfaces y cuentan con grandes matrices lógicas que se pueden programar mediante lenguajes de descripción de hardware como Verilog. A diferencia de los ASIC, cuyos procesos de diseño y control de calidad son muy largos, las FPGA ya disponen de homologación de calidad para la fabricación y se pueden diseñar en unos días o semanas. No obstante, las FPGA tradicionales se han considerado dispositivos demasiado grandes desde un punto de vista físico y con un consumo excesivo, por lo que están indicadas para aplicaciones embebidas cuyo consumo está limitado. Hasta ahora. La familia de FPGA CrossLink™ de Lattice Semiconductor proporcionan la combinación adecuada de rendimiento, tamaño y consumo para puentes de vídeo que utilicen Canales Virtuales. Ofrecen dos transceptores MIPI D-PHY de 4 carriles que llegan hasta 6 Gbps por PHY y un tamaño a partir de 6 mm2. Admiten hasta 15 pares de E/S diferenciales síncronos de fuente programable, entre ellos MIPI- D-PHY, LVDS, sub-LVDS e incluso CMOS paralelo de terminación sencilla, pero consumen menos de 100 mW en numerosas aplicaciones. La familia de FPGA CrossLink ofrece un modo de reposo cuya misión es reducir el consumo en espera. Lattice también suministra una completa biblioteca de IP de software con el objetivo de ayudar a los clientes a implementar con más rapidez diferentes tipos de soluciones de puenteo.

Resumen

Los Canales Virtuales que contempla la especificación MIPI CSI-2 (Camera Serial Interface-2) ayudan a los ingenieros de sistemas embebidos a concentrar varios flujos de datos de sensores a través de un solo puerto de E/S, reduciendo así el tamaño total del diseño y el consumo en aplicaciones que utilicen un gran número de sensores de imagen. Gracias a la reprogramabilidad, el rendimiento y el tamaño de FPGA de bajo consumo como la familia CrossLink de Lattice Semiconductor, los clientes pueden añadir Canales Virtuales a los diseños con sus dispositivos de forma rápida y sencilla.

Si quieres saber que es un sistema operativo haz clic en el enlace.