Las aplicaciones industriales y de automoción actuales se enfrentan a exigencias de rendimiento cada vez mayores. Las aplicaciones de potencia como los inversores para vehículos eléctricos (VE) y vehículos eléctricos ligeros (VEL), los motores CC sin escobillas, los convertidores CC-CC, los interruptores de potencia y los sistemas de gestión de baterías pueden disipar fácilmente varios kilovatios, lo que puede llevar a que los MOSFETs de silicio discretos individuales operan más allá de sus capacidades. Esto a menudo requiere conectar varios dispositivos en una configuración paralela para manejar eficazmente las altas demandas de corriente de estas aplicaciones. Este enfoque ayuda a evitar aumentos significativos de temperatura y a mantener condiciones de funcionamiento normales. Sin embargo, aunque generalmente es eficaz, tiene ciertos inconvenientes.

Este artículo explora estos desafíos y muestra cómo los MOSFETs de potencia de 100 V de Nexperia, alojados en el encapsulado CCPAK1212, pueden reducir el número de MOSFETs necesarios en paralelo para gestionar las altas demandas de corriente de las aplicaciones que consumen mucha energía, todo ello manteniendo un fuerte rendimiento térmico.

Consideraciones al conectar interruptores de potencia en paralelo

La primera desventaja asociada a la conexión de múltiples MOSFETs en paralelo es que puede dar lugar a un reparto desigual de la corriente entre los dispositivos. Esto se debe a las variaciones en la RDS(on) y otros parámetros dinámicos entre los dispositivos individuales, lo que significa que algunos terminan transportando más corriente que otros y, por lo tanto, experimentan mayores niveles de calentamiento. Con el tiempo, esto puede causar problemas de rendimiento y fiabilidad. Otro problema está relacionado con los tiempos de conmutación desiguales resultantes de las ligeras diferencias en el voltaje umbral (VGSTH) de los MOSFETs individuales, lo que puede conducir a una reducción de la eficiencia. Estas variaciones pueden atribuirse a tolerancias pequeñas pero inevitables que se producen durante el proceso de fabricación del silicio. Otra desventaja importante de este enfoque es el aumento de la lista de materiales y del espacio de PCB necesarios para la aplicación. Para los ingenieros de diseño de electrónica de potencia, minimizar el impacto de cada uno de estos problemas, sin comprometer el rendimiento térmico general de una aplicación, es un objetivo clave.

Comparación de MOSFETs conectados en paralelo en diferentes encapsulados

Nexperia realizó simulaciones térmicas en seis MOSFETs conectados en paralelo de 100 V 3,5 mΩ en encapsulados D2PAK (de un fabricante alternativo) que funcionaban como interruptores de carga en una aplicación típica de alta potencia de 48 V que debía manejar una corriente de carga continua de 50 A a una temperatura ambiente elevada de 120 °C (Figura 1).

Figura 1. Seis MOSFETs D2PAK con una superficie total de 1.107 mm2

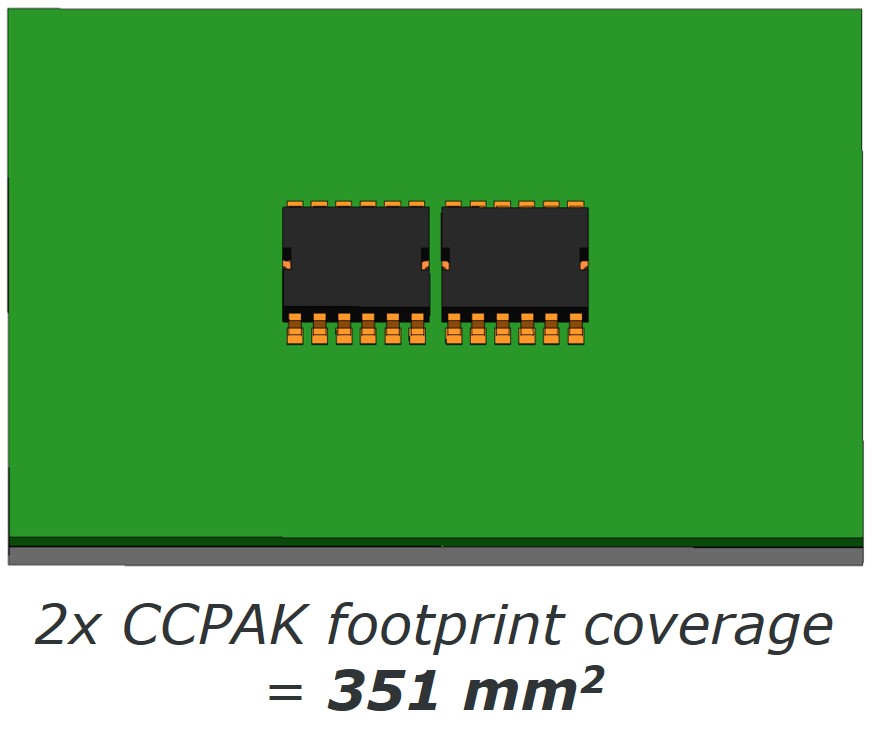

El propósito de esta investigación era comparar el rendimiento térmico de esta disposición paralela de seis interruptores con el de una aplicación idéntica implementada utilizando solo dos de los nuevos MOSFETs CCPAK1212 de 100 V de Nexperia conectados en paralelo, con una superficie total mucho menor de solo 351 mm2 (Figura 2).

Figura 2. Dos MOSFETs CCPAK1212 con una superficie total de 351 mm2

Para calcular las pérdidas de conducción I2R realistas para cada tipo de encapsulado, se utilizaron los valores especificados de RDS(on) a 150 °C para cada uno de los MOSFETs D2PAK y CCPAK1212. A esta temperatura, la resistencia total de dos CCPAK en paralelo es casi idéntica a la de seis MOSFETs en paralelo en un encapsulado D2PAK. Suponiendo un reparto de corriente igual entre los dispositivos (para una corriente total de 50 A), cada MOSFET CCPAK1212 conduce 25 A mientras que cada D2PAK conduce 8,33 A (Tabla 1). Estas cifras se utilizaron como base para las simulaciones térmicas realizadas en cada tipo de dispositivo.

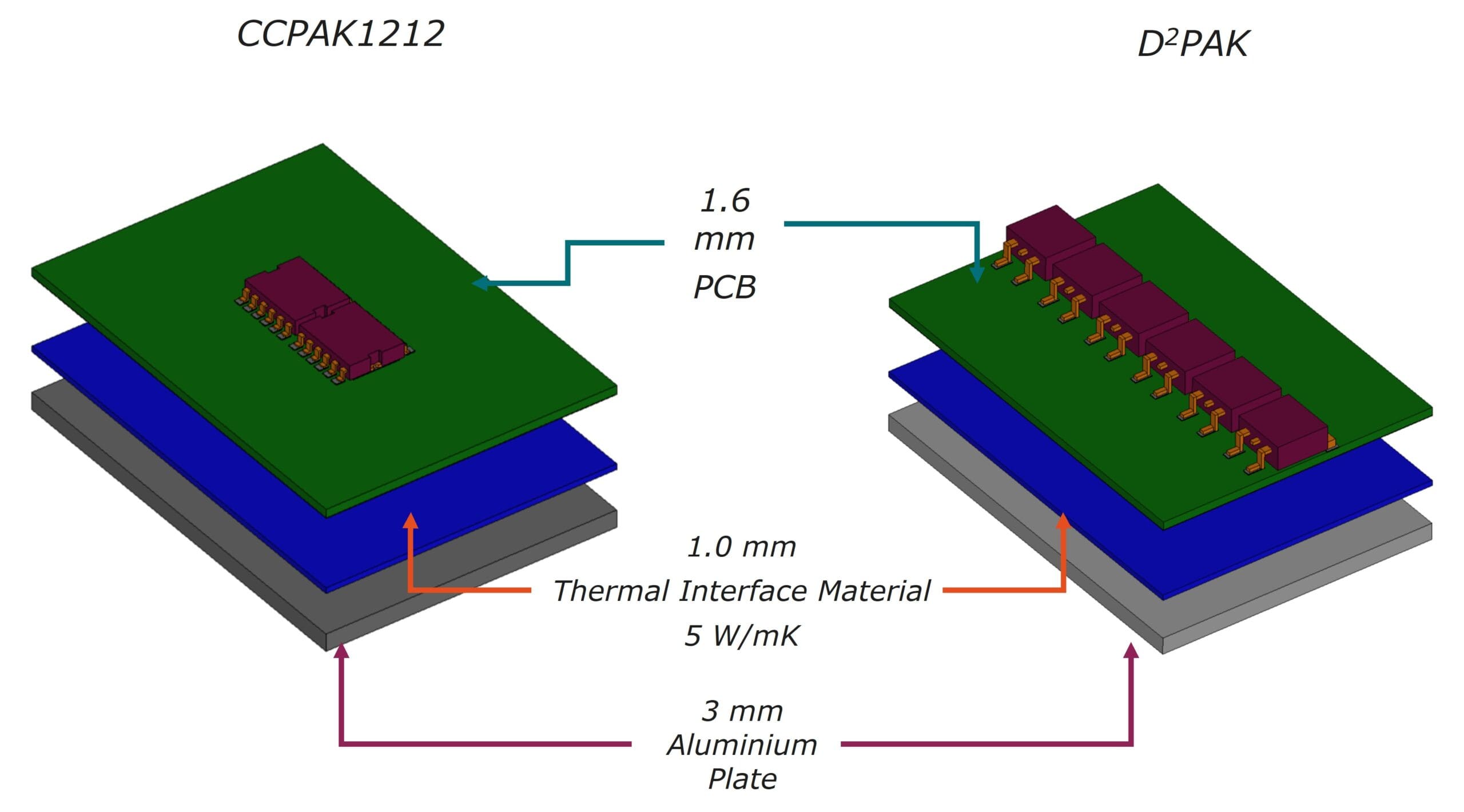

Estas simulaciones se basaron en una configuración realista de PCB (Figura 3) utilizando una PCB FR-4 de dos capas de 70 mm x 50 mm y 1,6 mm de grosor apoyada sobre una placa de aluminio de 3 mm de grosor con la misma superficie. La placa de PCB se separó con un material de interfaz térmica de 1 mm de grosor con una conductividad térmica de 5 W/mK.

Figura 3. Las simulaciones térmicas se basaron en configuraciones de PCB realistas para cada tipo de dispositivo

Para el apilamiento, el plano superior de cobre utilizó la huella de soldadura recomendada sin trazas adicionales y con 1 mm de separación entre los dispositivos, mientras que el plano inferior es un plano de cobre sólido, ya que la tierra está en ambos casos conectada en la parte superior e inferior con vías térmicas para mejorar la disipación. Por último, las redes de drenaje y fuente fueron aisladas eléctricamente.

Resultados del rendimiento térmico simulado

Los resultados de las simulaciones térmicas (Figura 4) mostraron que cada uno de los interruptores CCPAK1212 proporcionaba una temperatura de unión comparable y aumentos de temperatura de PCB equivalentes a los seis D2PAK en paralelo, al tiempo que reducía la cantidad de espacio de la placa en un 68%.

Figura 4. Dos interruptores CCPAK1212 conectados en paralelo ofrecen un rendimiento térmico equivalente en un área más pequeña

El excepcional rendimiento térmico (Figura 5) de estos interruptores puede atribuirse a la gran pastilla de silicio y al gran chasis de hilos de pinza de cobre que ofrece el encapsulado CCPAK1212.

Figura 5. Respuesta transitoria simulada para la temperatura de unión del dispositivo

En comparación con los encapsulados que utilizan hilos de unión, la mayor superficie de la pinza de cobre ofrece una mejor distribución de la corriente y reduce la posibilidad de formación de puntos calientes. Esto proporciona a los dispositivos una corriente máxima de funcionamiento más alta ID(max), un área de funcionamiento seguro (SOA) más grande y una resistencia térmica (Eas) más alta. Además, la resistividad de la pinza de cobre es aproximadamente un 40 % menor que la de los cables de unión de aluminio, lo que proporciona una RDS(on) eléctrica y una resistencia térmica (Rth(j-mb)) más bajas. El clip de cobre sólido y los tres pines de fuente paralelos proporcionan una menor inductancia (nH), permiten la eliminación de calor a través de los pines de fuente, facilitan la soldadura y ayudan a mejorar la fiabilidad a nivel de placa. La capacidad de eliminar el calor a través de los pines de fuente también ayuda a reducir la resistencia térmica.

Ventajas de las aplicaciones del CCPAK1212

MOSFETs alojados en este encapsulado proporcionen una conducción de alta corriente combinada con una inductancia parásita reducida y un excelente rendimiento térmico. Estas características los hacen ideales para su uso en aplicaciones de alto consumo energético como el control de motores, fuentes de alimentación y sistemas de energía renovable. La disponibilidad de opciones de refrigeración superior (TSC) e inferior (BSC) ofrece a los ingenieros una selección de técnicas de extracción térmica, que pueden ser útiles en aplicaciones en las que la disipación de calor a través de la PCB no es práctica debido a la sensibilidad de otros componentes. Además de los MOSFETs de potencia de 80 V y 100 V, Nexperia ofrece MOSFETs específicos para cada aplicación (ASFET) en CCPAK1212. Estos dispositivos están diseñados parala función de intercambio en caliente en servidores de inteligencia artificial (IA) cada vez más potentes, tienen un área de funcionamiento seguro (SOA) mejorada para proporcionar una estabilidad térmica superior durante las transiciones de modo lineal. Todos los MOSFETs= y ASFET CCPAK1212 de Nexperia están registrados en JEDEC y también están respaldados por las hojas de datos interactivas de Nexperia, que permiten a los diseñadores integrar estos dispositivos a la perfección en sus diseños.

Resumen

Los MOSFETs en encapsulado CCPAK1212 de Nexperia están diseñados para satisfacer las demandas térmicas de las aplicaciones industriales y de automoción de alta potencia de próxima generación. Este artículo demuestra cómo, en comparación con los MOSFETs en encapsulado D2PAK, pueden utilizarse para reducir el número de MOSFETs conectados en paralelo sin comprometer el rendimiento térmico de las aplicaciones de electrónica de potencia. La reducción del número de dispositivos conectados en paralelo ofrece varias ventajas de diseño, entre ellas la mitigación de los impactos de las tolerancias de fabricación en los tiempos de conmutación y reparto de corriente. Además, el uso de menos dispositivos también ayuda a simplificar los requisitos de los circuitos de conducción, al tiempo que reduce significativamente el espacio necesario en la placa y la lista de materiales asociada.