Recientemente, Renesas ha ampliado su popular familia de microprocesadores (MPU) RZ con un nuevo dispositivo destinado a aplicaciones robóticas de alto rendimiento. Al ofrecer un rendimiento superior dentro de la familia, el nuevo microprocesador RZ/V2H permite control en tiempo real e inteligencia artificial IA de visión. El nuevo MPU RZ/V2H también será un punto destacado en el stand de Renesas en Embedded World de este año en el Pabellón 1, Stand 234 (1-234). Tuvimos la oportunidad de hablar con Keigo Kawasaki, director de marketing de Renesas, sobre la nueva incorporación a la familia RZ y sus nuevas características únicas para el área de aplicaciones de robótica para una mayor evolución de la IA.

P: Cada vez más empresas de semiconductores ofrecen procesadores de IA. ¿Qué diferencia a Renesas de la competencia?

Hay tres PVU a destacar:

- Acelerador de IA “DRP-AI 3” con tecnología de “poda”: la poda es un enfoque basado en hardware para habilitar modelos de IA ligeros y mejorar la eficiencia informática de la IA. Esto también afecta en una eficiencia energética de 10 TOPS/W, con lo que se consigue una mejora 10 veces mayor que los modelos anteriores.

- Aceleración del procesamiento de imágenes además de la aceleración de IA: para aumentar el rendimiento de todo el sistema de imágenes, el RZ/V2H incluye el acelerador OpenCV, junto con la biblioteca de aceleración OpenCV gratuita.

- Además Arm Cortex-A55 con cuatro núcleos de 1,8 GHz para aplicaciones en las que se requiere un rendimiento robusto de control en tiempo real con tres procesadores Cortex-R8 de doble núcleo de 800 MHz y un procesador Cortex-M33 para manejar tareas menos intensivas, como la lectura de datos de sensores. El nuevo RZ/V2H de Renesas es el único procesador de IA heterogéneo que está equipado con los tres productos Cortex (A, R, M) de Arm.

P: ¿Cuáles son los desafíos para implementar la visión AI, especialmente en sistemas integrados? ¿Cuál es la solución de Renesas?

La generación de calor es un desafío importante en los sistemas integrados. Dado que los procesadores de alto rendimiento generan calor, los ingenieros a menudo enfrentan desafíos para compensar el calor, ya sea reduciendo el rendimiento o agregando componentes que disipen el calor, lo que a su vez aumenta el costo y el tamaño del sistema. Con Renesas RZ/V2H, pueden alcanzar fácilmente un rendimiento de 10 TOPS/W sin ventiladores de refrigeración.

P: ¿Qué aplicaciones requieren procesamiento de imágenes en tiempo real?

Por un lado, robots industriales para la automatización de fábricas y robots de servicios para restaurantes e instalaciones comerciales. Se trata de robots que pueden reconocer objetos y obstáculos circundantes en tiempo real y moverse de forma autónoma. Por otro lado, los drones y los pequeños vehículos de transporte también necesitan pensar de forma independiente y operar en tiempo real. El RZ/V2H es ideal para estas aplicaciones.

P: ¿Qué tipo de comentarios recibió de los clientes?

Muchos clientes ya han decidido adoptar nuestros módulos de IA para aplicaciones industriales y pequeños módulos HSR (Human Support Robot). También hay más de 40 clientes que están considerando nuestros productos. El factor decisivo en todas estas negociaciones es el hecho de que el RZ/V2H puede reducir significativamente la generación de calor.

P: ¿Qué acelera la adopción generalizada de aplicaciones de IA de visión? ¿Cuál es la estrategia de Renesas?

Un desafío importante es que los ingenieros a menudo tienen dificultades para utilizar la IA de manera efectiva debido a la necesidad de habilidades especializadas en IA. Renesas ofrece una serie de bibliotecas de aplicaciones de IA de forma gratuita para abordar los desafíos de los clientes.

P: Cuéntenos sobre su hoja de ruta futura.

En el frente tecnológico, continuaremos buscando TOPS/W para mejorar el rendimiento energético. En el futuro, esperamos que los dispositivos integrados tengan aplicaciones que requieran más rendimiento informático, como la IA generativa. En términos de búsqueda de nuevos productos, continuaremos abordando las demandas de nuestros clientes y del mercado.

P: ¿Cuáles son los beneficios de la tecnología DRP patentada de Renesas?

DRP (procesador dinámicamente reconfigurable) puede ejecutar aplicaciones mientras cambia dinámicamente la configuración de conexión del circuito de las unidades aritméticas en el chip en cada reloj operativo de acuerdo con el contenido a procesar. Dado que sólo se utilizan los circuitos aritméticos necesarios, el DRP consume menos energía que el procesamiento de la CPU y puede alcanzar una mayor velocidad. Además, en comparación con las CPU, donde los accesos frecuentes a la memoria externa debido a errores de caché y otras causas degradarán el rendimiento, el DRP puede crear las rutas de datos necesarias en el hardware con anticipación, lo que resulta en una menor degradación del rendimiento y una menor variación en la velocidad de operación (jitter). debido a los accesos a la memoria.

El DRP también tiene una función reconfigurable dinámica que cambia la información de conexión del circuito cada vez que cambia el algoritmo, lo que permite el procesamiento con recursos de hardware limitados, incluso en aplicaciones robóticas que requieren el procesamiento de múltiples algoritmos.

El DRP es particularmente eficaz en el procesamiento de datos en streaming, como el reconocimiento de imágenes, donde la paralelización y la canalización mejoran directamente el rendimiento.

P: ¿Cuáles son los beneficios de una arquitectura heterogénea en la que DRP-AI 3, DRP y la CPU funcionan de forma cooperativa?

R: Los robots de servicio, por ejemplo, requieren un procesamiento avanzado de IA para reconocer el entorno circundante. Por otro lado, también se requiere un procesamiento basado en algoritmos que no utilice IA para decidir y controlar el comportamiento del robot. Sin embargo, los procesadores integrados (CPU) actuales carecen de recursos suficientes para realizar estos diversos tipos de procesamiento en tiempo real. Renesas resolvió este problema desarrollando una tecnología de arquitectura heterogénea que permite que el procesador dinámicamente reconfigurable (DRP), el acelerador de IA (DRP-AI) y la CPU trabajen juntos.

DRP AI acelera el procesamiento de la visión AI. Renesas ha aplicado su tecnología DRP patentada para desarrollar el acelerador OpenCV que acelera el procesamiento de OpenCV, una biblioteca estándar de la industria de código abierto para el procesamiento de visión por computadora. La mejora de velocidad resultante es hasta 16 veces más rápida en comparación con el procesamiento de la CPU. La combinación de DRP-AI y OpenCV Accelerator mejora tanto la computación de IA como los algoritmos de procesamiento de imágenes, lo que permite la ejecución en tiempo real y con eficiencia energética de Virtual SLAM utilizado en aplicaciones como robots aspiradores.

Por otro lado, programas como la decisión y el control del comportamiento de los robots requieren procesamiento mientras cambian las condiciones y procesan detalles en respuesta a los cambios en el entorno circundante. El procesamiento de software de la CPU puede ser más adecuado para esto que el procesamiento de hardware como en el DRP. Es importante distribuir el procesamiento en los lugares correctos y operar de manera coordinada. La tecnología de arquitectura heterogénea de Renesas permite que DRP y CPU trabajen juntos.

P: ¿Renesas tiene planes de desarrollar una Unidad de Procesamiento Neural (NPU)?

“NPU” es un término genérico para IP de hardware especializado para el procesamiento de IA, y DRP-AI es un tipo de NPU.

P: ¿Cuáles son las nuevas tecnologías aplicadas DRP-AI 3 incorporadas en RZ/V2H?

R: DRP-AI3 introduce nuevos métodos de alta velocidad y bajo consumo que admiten los principales métodos básicos de modelos de IA. Específicamente, se admiten los siguientes métodos básicos:

1) Cuantización: pesos de bits más bajos para la información de peso de la red neuronal (peso) y los datos de entrada/salida (mapa de características) para cada capa. Cambio de la aritmética de punto flotante de 16 bits en DRP-AI convencional a la aritmética de enteros de 8 bits (INT8).

2) Corte de ramas: una técnica para omitir cálculos estableciendo en cero la información de peso (ramas) que no afecta la precisión del reconocimiento.

Se presentó contenido técnico más detallado en ISSCC 2024 (Conferencia Internacional de Circuitos de Estado Sólido 2024), la principal conferencia internacional sobre circuitos semiconductores, celebrada del 18 al 22 de febrero de 2024. El comunicado de prensa se publicó el 22 de febrero de 2024.

P: ¿Hay alguna combinación ganadora para RZ/V2H ya disponible?

R: Renesas ha desarrollado la «Computadora de placa única con detección visual» que utiliza imágenes de cámaras para identificar su entorno y determinar y controlar sus movimientos en tiempo real. Esta solución combina el RZ/V2H con circuitos integrados de administración de energía y generadores de reloj programables VersaClock para respaldar robots y maquinaria industriales energéticamente eficientes. Su diseño eficiente elimina la necesidad de un ventilador de refrigeración adicional, lo que mantiene la lista de materiales y el tamaño de la solución reducidos.

Esta combinación ganadora se exhibirá en el stand de Renesas en Embedded World 2024 en el Pabellón 1, Stand 234 (1-234).

P: ¿Qué pasa con la gama de la serie RZ/V?

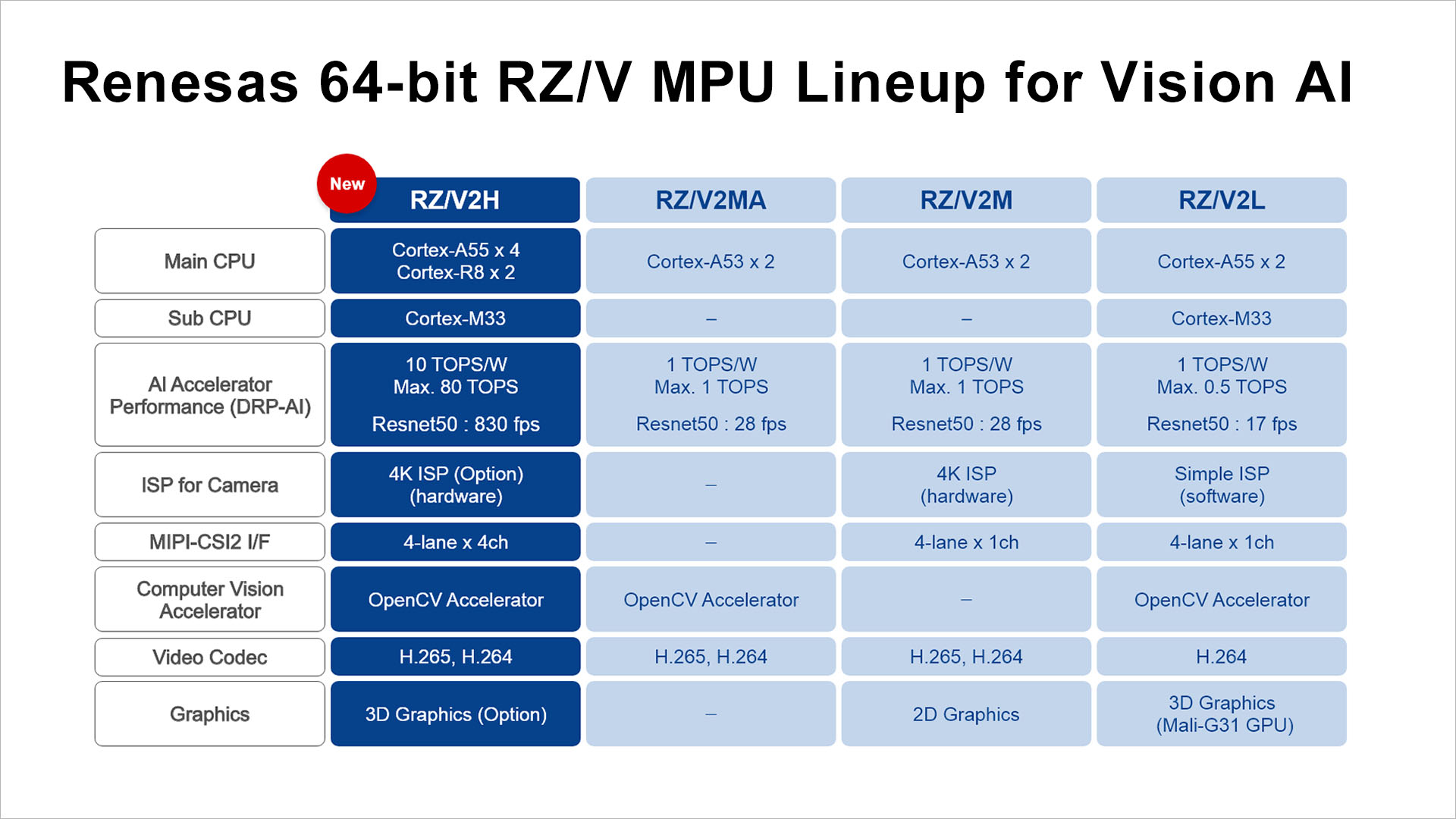

R: La serie RZ/V son MPU que incorporan un acelerador DRP-AI. Hay una línea escalable desde 0,5 TOPS hasta 80 TOPS con la misma arquitectura.