MEN ha desarrollado una nueva placa VME con procesador Intel Xeon D para CERN. Gracias a una FPGA-based PCIe-VME64x bridge de código abierto, el equipamiento existente del acelerador de partículas ahora puede actualizarse con un procesador más actual y permanecer en funcionamiento durante muchos años. El plan es utilizar VME hasta el final programado de LHC en 2032.

CERN es el centro de investigación más grande del mundo en el campo de la física de partículas, cuyos cimientos se remontan a 1954. Hoy en día, más de 2.500 empleados y más de 12.000 científicos visitantes de 85 naciones están investigando allí los bloques de construcción de nuestro Universo. Probablemente el más conocido es el Gran Colisionador de Hadrones (LHC) de 27 kilómetros de largo, que entró en funcionamiento en 2008. Una de las preguntas que ayuda a examinar, es por qué nuestro Universo consiste principalmente en materia y no en partes iguales también de antimateria. El equipo más avanzado se utiliza para esta y muchas otras tareas, y se realizan enormes inversiones año tras año. También es muy importante mantener la infraestructura existente durante los próximos años.

Dispositivos flexibles para adquisición de datos y control de aceleradores

Tomemos, por ejemplo, los miles de las llamadas cajas que se han instalado en los numerosos aceleradores de partículas en el CERN durante años. Desplegados en la infraestructura de soporte de varios detectores de partículas, generalmente se usan para la electrónica de activación y la adquisición de datos. Las cajas tienen una configuración típica basada en ranuras con backplane y módulos configurables libremente. Este tipo de sistema electrónico modular está predestinado para su uso en instituciones científicas como el CERN, ya que dichos sistemas modulares permiten que los circuitos individuales se reutilicen muchas veces y se implementen en múltiples sistemas y en varias configuraciones. Una vez que se termina un experimento, las cajas se reutilizan para nuevos experimentos en diferentes configuraciones, lo que asegura la inversión inicial a largo plazo. Un tipo de estas cajas se basa en el bus VME, que se especificó por primera vez en 1981 y se ha desarrollado continuamente desde entonces. Actualmente, más de 900 cajas de este tipo están en uso en el propio CERN, principalmente para controlar los aceleradores. Se utilizan cajas en diferentes configuraciones para la adquisición de datos en los experimentos y detectores. En el experimento LHCb, por ejemplo, se utilizan para pre-procesar partes de los datos nativos de aproximadamente un millón de sensores para que los científicos reciban solo los datos relevantes para sus análisis. Otras cajas se encuentran en muchos otros detectores CERN como ATLAS, CMS, ALICE, ISOLDE y TOTEM, en algunos casos cumplen tareas completamente diferentes, ya que, al igual que cualquier otro sistema de backplane modular, se pueden usar de manera extremadamente flexible.

Nuevos dispositivos para nuevos retos

Dado que las tareas cambian con cada experimento, constantemente se desarrollan nuevas configuraciones de cajas que deben proporcionar lo último en rendimiento informático. Solo en 2016, y en los aceleradores, se pusieron en funcionamiento alrededor de 50 cajas nuevas. Además, ya es previsible que se instalen alrededor de 200 cajas nuevas durante el “Long Shutdown” planificado de 2019 a 2020, que se usará para reparar y revisar completamente los equipos. Sin embargo, un problema con los sistemas basados en VME radica en el hecho de que los procesadores no admiten de forma nativa la comunicación a través del bus VME. Por lo tanto, las placas procesadoras deben proporcionar un puente PCIe-VME64x para interactuar con el bus VME. Sin embargo, solo algunos fabricantes disponían de componentes discretos, mientras que el proveedor principal había anunciado el fin de la vida útil del componente actual (TSI148). La dimensión de este problema se aclara rápidamente al considerar la cantidad de ordenadores monoplaca (SBC) con el bus VME instalado en el CERN: en la actualidad, están instalados más de 900 SBC basados en VME de MEN Mikro Elektronik con Intel® Core™ Duo y Core™ 2 Duo. Si bien estas son cantidades significativas para las placas VME de alta calidad, este volumen por sí solo no justificaría la fabricación de un componente discreto solo para este propósito. Por lo tanto, el Beams Department / Control Group del CERN, BE / CO para abreviar, estaba buscando alternativas sostenibles para los próximos años mediante la publicación de una nueva licitación.

En busca de una nueva solución para el bus VME64x

Se especificaron tres opciones posibles para la comunicación de PCI / PCIe a VME64x. tener un stock suficiente de chips TSI148 para poder producir la cantidad de placas especificadas en el contrato, o utilizar el Tundra Universe II, el predecesor del TSI148, o utilizar la tecnología FPGA: en ese caso, el CERN solicitó a los licitadores que pusieran a disposición las fuentes VHDL completas para el diseño de FPGA a través de una licencia GPL3 o posterior. Además de las dos primeras opciones, el CERN sabía que había compañías con implementaciones patentadas de puentes VME realizadas en FPGA. Por ejemplo, las generaciones anteriores de SBC utilizados en CERN (antes de las placas basadas en TSI148) tenían un procesador PowerPC con una FPGA para conectarse a un bus VME. Por lo tanto, con la última opción en la convocatoria de licitación, el CERN esperaba que al menos una de estas empresas estuviera lista para su implementación de código abierto. Por otro lado, para garantizar condiciones justas para cualquiera que presente sus ofertas, el CERN no dio preferencia a ninguna de estas opciones. La selección se basó en el precio de las ofertas presentadas en la licitación. Finalmente, se eligió a la compañía que ofrecía los mejores precios para que se le adjudicara el contrato.

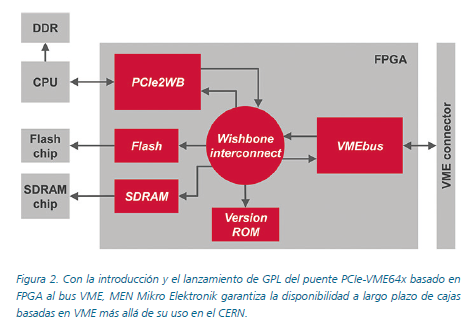

El puente de código abierto PCIe-VME64x ya está disponible

El resultado de esa licitación conduce a una solución basada en la tecnología FPGA y, por lo tanto, todas las fuentes VHDL ahora están disponibles bajo la licencia GPL3 o posterior, y el paquete de controladores de Linux bajo la licencia GPL2 o posterior en la página del proyecto puente PCIe-a- VME del Repositorio de Hardware Abierto. El puente open source PCIe-a-VME es un gran paso no solo para el CERN, sino también para todas las demás instituciones alrededor del mundo donde VME todavía está en uso. En primer lugar, los ingenieros del CERN ya no dependen de un proveedor en particular. Incluso si el chip FPGA que se usa actualmente se vuelve obsoleto, el acceso a las fuentes VHDL completas les permite portar el puente de PCIe a VME a otro FPGA. Gracias al hecho de que el diseño es de código abierto, cualquier instituto o empresa ahora no solo puede comprar un producto actualizado con ese puente, sino que también puede construir cualquier otro SBC de VME utilizando el mismo puente. El uso del mismo puente VME en SBC significa también los mismos controladores del kernel de Linux y la API VME de usuario para todos los institutos y empresas. En el futuro, esto debería permitir a todos los ingenieros colaborar más eficientemente en el mundo VME y tener más libertad para compartir y reutilizar los controladores del kernel de Linux para las placas VME que, por ejemplo, los ingenieros del CERN diseñan por su cuenta.

Colaborador de la nueva lógica FPGA

La empresa que estaba abierta a invertir un gran esfuerzo junto con el CERN para diseñar, probar y validar un puente PCIe Gen 3 adecuado para los sistemas de 64 bits de VME fue MEN Mikro Elektronik. La compañía no solo trabajó junto con el equipo de CERN en la validación y las pruebas, sino también en el código abierto, publicando el puente de PCIe a VME que traduce las operaciones de lectura y escritura en el espacio de direcciones de PCIe para leer y escribir transacciones en el bus VME. Actúa como un punto final PCIe en un lado y un bus maestro VME en el otro. El puente puede generar ciclos únicos de VME y transferencias de bloques.

Actualmente se admiten los siguientes tipos de acceso: Ciclos únicos de VME: A16, A24, A32 con cualquiera de los anchos de datos D8, D16, D32 Transferencias de bloques VME (BLT): A24D16, A24D32, A32D32 más la transferencia de bloques multiplexada (MBLT) A24D64 y A32D64 Acceso al espacio de configuración CR / CSR Las transferencias de bloques VME se ejecutan mediante un motor de acceso directo a memoria (DMA), donde los bloques de datos se transfieren entre la memoria del sistema y el bus VME, sin pasar por la CPU. Además, también es posible usar DMA con ciclos individuales, lo que es especialmente útil para las placas conectadas que no admiten el modo de acceso BLT. En general, esta es una forma más rápida y más eficiente de intercambiar varias palabras de datos, ya que la CPU es libre de continuar su funcionamiento normal hasta que el motor DMA termina con una tarea programada. El puente también admite algunas características agregadas en las extensiones VME64x.

Puede usar los pines de la dirección geográfica y generar un tipo especial de acceso A24 para leer y escribir el espacio de configuración CR / CSR de los esclavos VME instalados en la misma caja. Sin embargo, aunque ninguno de los modos de transferencia rápida (2eVME, 2eSST) son compatibles actualmente, estos podrían implementarse en el futuro ya que las próximas tarjetas esclavas VME pueden requerirlos; Este tema ya está siendo evaluado en MEN. Además, el módulo de bus VME implementado por MEN puede actuar tanto como maestro VME como esclavo VME. Esto permite no solo su uso en SBCs VME que se ejecutan como maestros, sino también para aprovecharlos en E / S y otras tarjetas periféricas conectadas como esclavos. Aunque para la aplicación de SBC VME, la configuración se centra solo en la funcionalidad maestra de VME. Actualmente, todo el diseño de puente ocupa solo el 30 por ciento del área FPGA del Intel Cyclone. Esto significa que hay mucho espacio disponible para implementar nuevas funciones adicionales (como 2eVME, transferencias 2eSST).

Disponibilidad a largo plazo garantizada

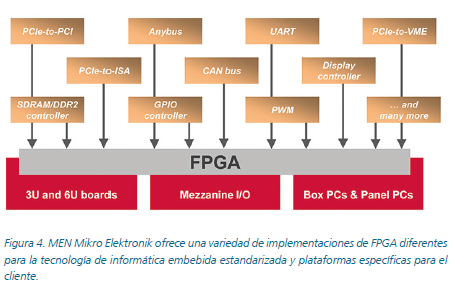

Al lanzar la especificación junto con el despliegue de las primeras placas con el nuevo puente PCIe a VME64x basado en FPGA, el CERN ha alcanzado un hito importante para la disponibilidad a largo plazo de sus cajas basadas en VME para la adquisición de datos y el control del acelerador. La referencia también es un hito para todos los demás usuarios existentes de sistemas basados en VME, porque la disponibilidad de la lógica adecuada ahora también está garantizada para ellos a largo plazo. Según las estimaciones actuales, el mercado para las nuevas placas aún ascenderá a más de 200 millones de dólares USD en 2020. Durante el proyecto, el especialista en informática embebida MEN Mikro Elektronik demostró una vez más su gran experiencia en tecnología FPGA e informática embebida estandarizada junto a los conocimientos de la CPU VME. Con el puente PCIe-a-VME, los clientes se benefician de la disponibilidad a largo plazo de las instalaciones existentes. MEN Mikro Elektronik también puede ofrecer soluciones customizadas a cada tipo de cliente, por ejemplo, PCIe a PCI o incluso PCIe a ISA, que también hacen que el hardware heredado de los OEMs esté disponible a largo plazo, lo que proporciona un retorno de la inversión aún más prolongado. Junto a las soluciones de puente para buses heredados internos para asegurar la disponibilidad a largo plazo, la compañía también ofrece puentes basados en FPGA a interfaces y buses externos, como UART, bus CAN o controladores QSPI utilizando SPI.

Este escenario permite a los clientes OEM crear variantes de forma extremadamente rentables. Por ejemplo, un solo diseño de una tarjera CPU se puede utilizar para aplicaciones completamente diferentes. Incluso cuando los tamaños de los lotes son pequeños, es posible atender significativamente más aplicaciones, como soluciones con diferentes buses de campo o variantes de Ethernet industrial, o, específicamente, soluciones con requisitos de migración, por ejemplo, en ingeniería ferroviaria o construcción de aeronaves. Los OEM pueden utilizar una única plataforma de hardware en todas las variantes, lo que simplifica significativamente el servicio, la documentación y la certificación.

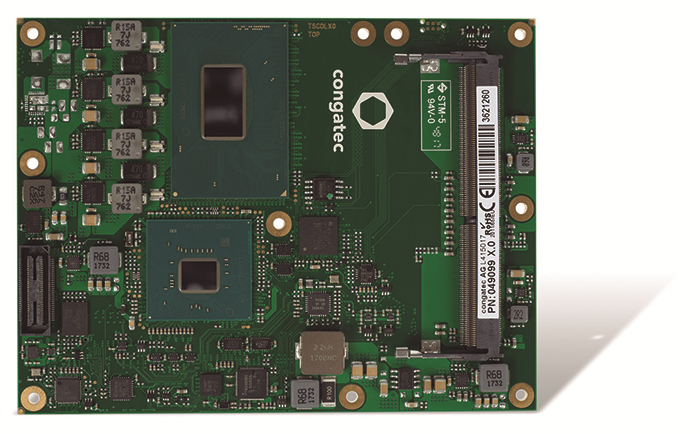

La primera placa con el nuevo puente

La primera placa con el nuevo puente basado en FPGA para el bus VME y utilizada en el CERN es la A25 de MEN Mikro Elektronik. Está equipada con la CPU Xeon D-1500 de Intel y, además del nuevo FPGA, combina una alta eficiencia de costes con un rico conjunto de características. Además, el A25 admite la reducción del tamaño del sistema, el funcionamiento fiable a largo plazo sin refrigeración forzada por aire y las múltiples funciones de cálculo con una sola placa. Con dos puertos USB 3.0, hasta tres puertos Gigabit Ethernet y dos RS232 COM en la parte frontal, la placa ofrece los fundamentos básicos de un ordenador industrial multiuso.

Al estar equipado con hasta 8 GByte de DDR4 SDRAM con ECC acompañado de Flash, la necesidad de ampliaciones de almacenamiento masivo flexibles está cubierta por ranuras para microSD y mSATA. Además, la A25 se puede equipar con una tarjeta intermedia XMC / PMC y una tarjeta mini PCI Express, que proporcionan E / S frontales adicionales (XMC / PMC) para funciones como gráficos, almacenamiento masivo o puertos Ethernet adicionales. La ranura PMC admite módulos de PCI-X de hasta 64 bits / 133 MHz, mientras que la ranura XMC está controlada por un enlace PCI Express x8. La ampliación modular con mezzanines de E / S en un ordenador monoplaza permite configurar sistemas personalizados a partir de componentes estándar abiertos, lo que reduce el tiempo y el coste de la integración. El A25 admite el funcionamiento en un rango de temperatura desde -40°C a +60°C. La resistente placa soporta golpes y vibraciones ya que todos los componentes de la placa están soldados, lo cual es un requisito previo para un funcionamiento fiable y una vida útil más larga del producto.