Autor: Grant Floyd, product marketing manager de Microchip Technology

Introducción/Problema

Una vida útil más larga y una mayor fiabilidad de los productos se están convirtiendo en características cada vez más deseables. Los consumidores esperan productos electrónicos, electrodomésticos y otros dispositivos de mayor calidad y más fiables con un precio más ajustado. Muchas de estas aplicaciones incluyen componentes electrónicos embebidos que contienen memoria integrada, como Flash o EEPROM. Como saben los diseñadores de sistemas, la memoria Flash y la EEPROM no tienen una resistencia ilimitada al borrado y la escritura, pero, aun así, estas memorias son necesarias para almacenar datos durante el funcionamiento y cuando el sistema está apagado. Por lo tanto, se ha generalizado el uso de técnicas de reducción del desgaste que pueden aumentar considerablemente la longevidad de la memoria integrada. Un método común de reducción del desgaste es el denominado «nivelación de desgaste» ó «wear-leveling».

Wear-Leveling

Cuando se utiliza EEPROM en un diseño, es fundamental tener en cuenta su resistencia, que suele ser de 100.000 ciclos para la EEPROM integrada en un MCU y de 1 millón de ciclos para la EEPROM independiente a temperatura ambiente. Los diseñadores deben tener esto en cuenta estimando el número de ciclos de borrado/escritura durante la vida útil típica de la aplicación (a veces denominada perfil de misión) para determinar el tamaño de la EEPROM que necesitan y cómo asignar los datos dentro de la memoria.

Por ejemplo, en un sistema comercial de medición de agua con cuatro sensores para diferentes áreas de un edificio, cada sensor genera un paquete de datos por sesión de uso, registrando el volumen de agua, la duración de la sesión y las marcas de tiempo. Los paquetes de datos almacenados en la EEPROM se añaden con los datos actualizados cada vez que se produce una nueva sesión hasta que el paquete se llena. Los datos se almacenan en la EEPROM hasta que un servidor central solicita su extracción. El sistema está diseñado para extraer los datos con la frecuencia suficiente para evitar sobrescribir los datos existentes dentro de cada paquete. Suponiendo una vida útil de 10 años y una media de 400 paquetes diarios por sensor, el total de ciclos por sensor alcanzará los 1,46 millones, superando la resistencia típica de la EEPROM. Para solucionar esto, puede crear una rutina de software para distribuir el desgaste entre los bloques adicionales (suponiendo que disponga de espacio sobrante). Esto se denomina nivelación del desgaste.

Entonces, ¿cómo se implementa esto?

Para implementar la nivelación del desgaste en esta aplicación, puede adquirir una EEPROM con el doble de capacidad, lo que le permitirá asignar 2 bloques a cada sensor (para un total de 2 millones de ciclos disponibles por sensor). Esto proporciona un búfer de ciclos adicionales en caso de necesidad (540.000 ciclos adicionales para cada sensor en este ejemplo).

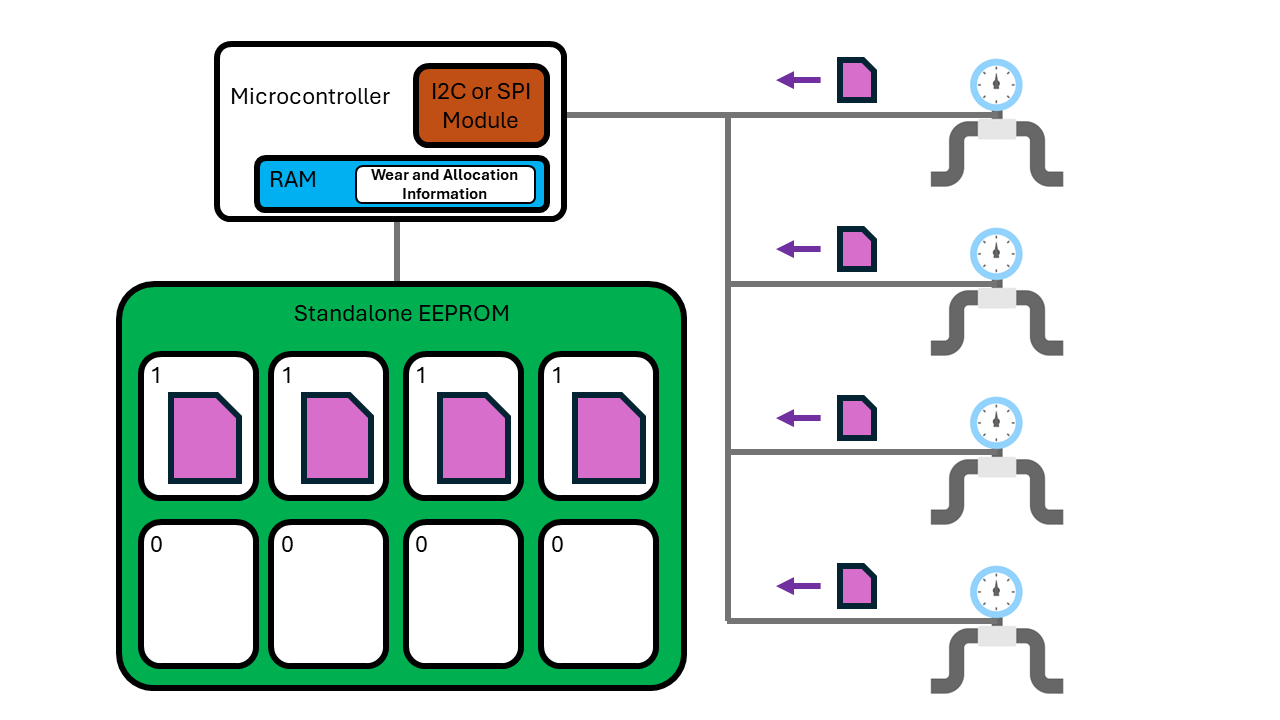

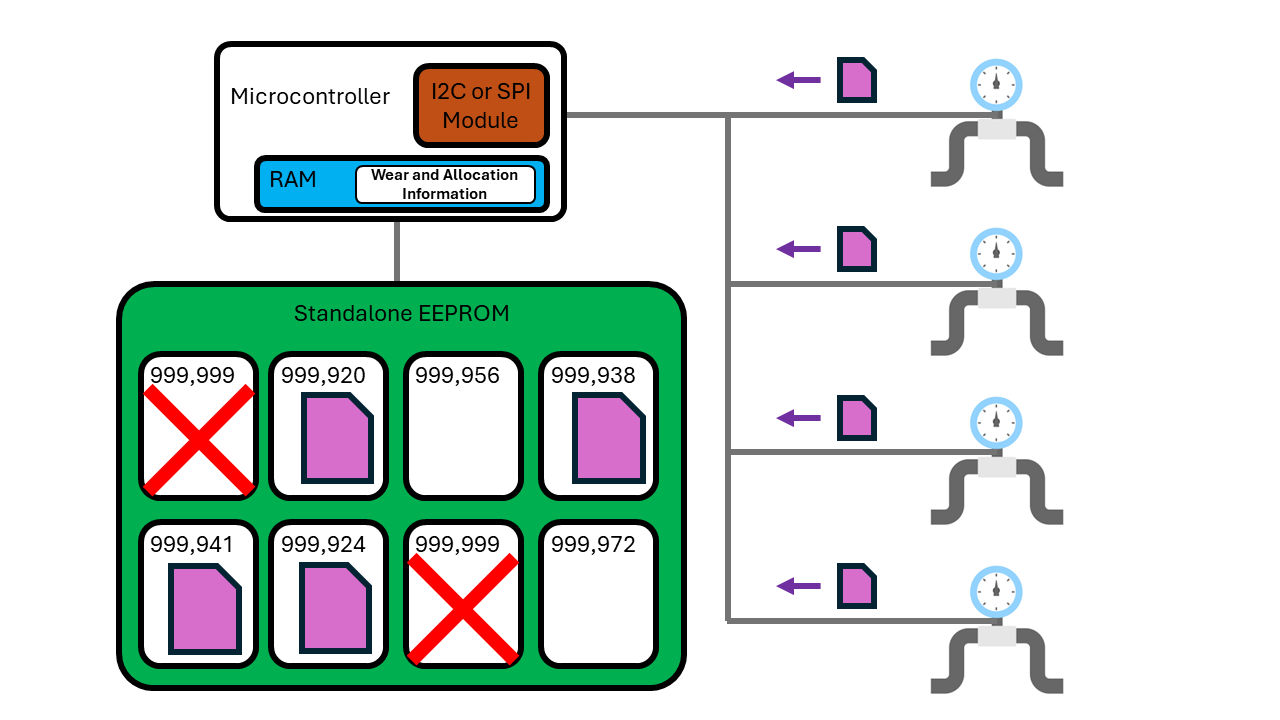

A continuación, necesitará alguna forma de saber dónde escribir los nuevos datos para distribuir el desgaste. Aunque podría escribir cada bloque hasta su límite de 1 millón de ciclos antes de pasar al siguiente, este enfoque podría provocar un desgaste prematuro si algunos sensores generan más datos que otros. Si distribuye el desgaste de forma uniforme en toda la EEPROM, la aplicación en su conjunto durará más tiempo. La figura 1 ilustra el ejemplo explicado anteriormente, con cuatro contadores de agua que envían paquetes de datos (en morado) al MCU a través del bus de comunicación. Los datos se almacenan en bloques dentro de la EEPROM. Cada bloque tiene un contador en la parte superior izquierda que indica el número de ciclos de borrado-escritura que ha experimentado.

Figura 1. Contador de agua comercial, paquetes de datos almacenados en la EEPROM, la EEPROM tiene el doble de espacio del necesario

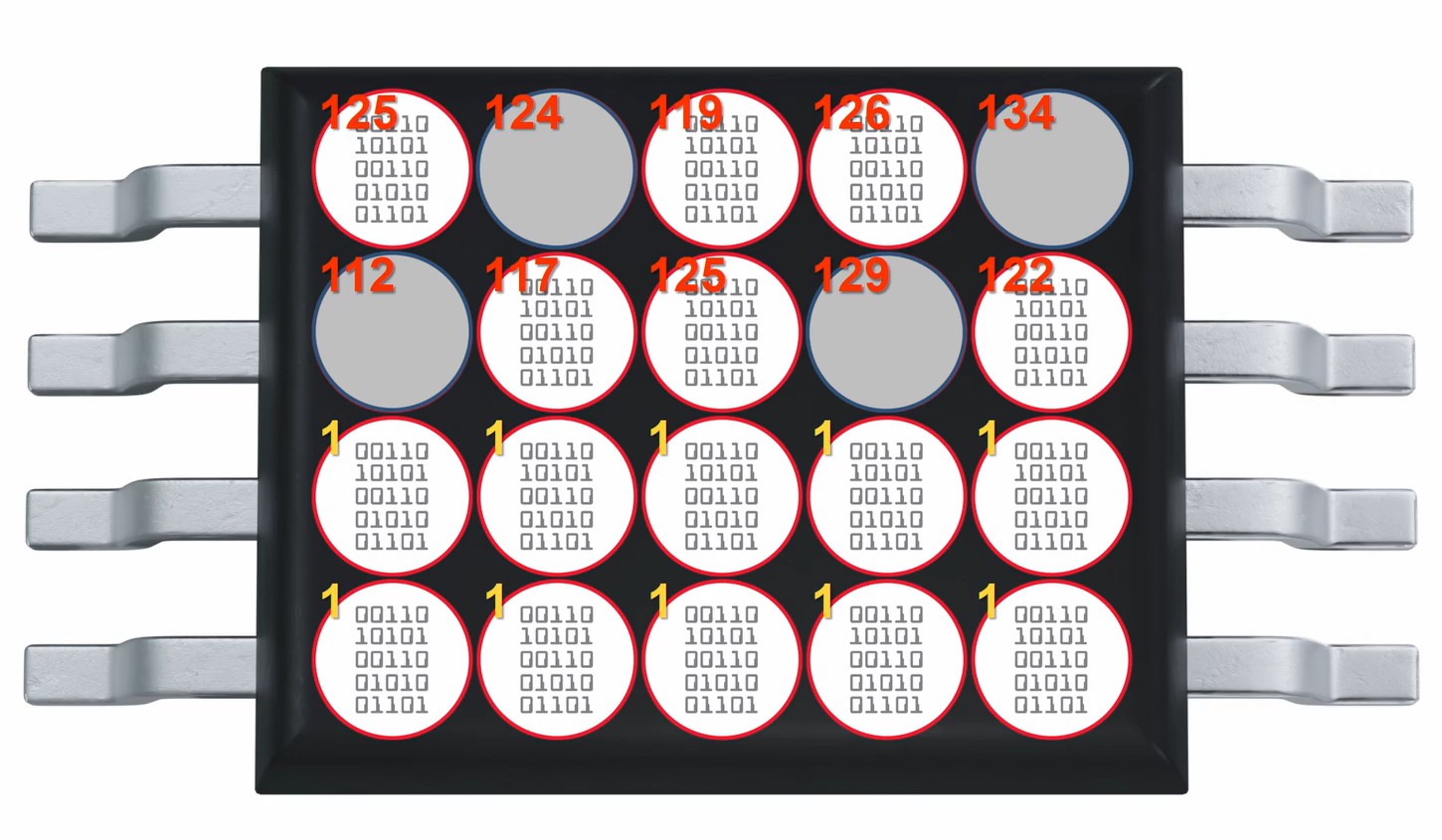

Hay dos tipos principales de nivelación del desgaste: dinámica y estática. La dinámica es más básica y es la mejor para distribuir el desgaste en un espacio pequeño de la EEPROM. Distribuye el desgaste entre los bloques de memoria cuyos datos cambian con más frecuencia. Es más fácil de implementar y requiere menos sobrecarga, pero puede dar lugar a un desgaste desigual, lo que puede ser problemático, como se ilustra en la figura 2.

Figura 2. Fallo en la distribución uniforme del desgaste

La nivelación de desgaste estática distribuye el desgaste por toda la EEPROM, lo que prolonga la vida útil de todo el dispositivo. Se recomienda si la aplicación puede utilizar toda la memoria como almacenamiento (por ejemplo, si no se necesita parte del espacio para almacenar datos vitales que no cambian) y producirá la mayor resistencia durante la vida útil de la aplicación. Sin embargo, es más compleja de implementar y requiere más sobrecarga de la CPU.

La nivelación del desgaste requiere supervisar los ciclos de borrado/escritura de cada bloque de memoria y su estado de asignación, lo que en sí mismo puede causar desgaste en la memoria no volátil (NVM). Hay muchas formas inteligentes de manejar esto, pero para simplificar, supongamos que almacena esta información en la RAM de su MCU, que no se desgasta. La RAM pierde datos cuando se produce un corte de alimentación, por lo que deberá diseñar un circuito alrededor de su MCU para detectar el inicio de la pérdida de alimentación y tener tiempo de transferir los estados actuales del registro a la NVM.

En un enfoque de software para la nivelación del desgaste, la idea general es crear un algoritmo que dirija la siguiente escritura al bloque con el menor número de escrituras para distribuir el desgaste. En la nivelación de desgaste estática, cada escritura almacena los datos en la ubicación menos utilizada que no está asignada actualmente a nada más. También intercambia los datos a una nueva ubicación sin usar si el número de ciclos entre el bloque más utilizado y el menos utilizado es demasiado grande. El número de ciclos que ha pasado cada bloque se registra con un contador y, cuando el contador alcanza la resistencia máxima, se considera que ese bloque ha alcanzado su vida útil prevista y se retira.

Figura 3. Nivelación del desgaste que prolonga la vida útil de la EEPROM en la aplicación, incluidos los bloques de memoria que se han retirado (X rojas).

La nivelación del desgaste es un método eficaz para reducir el desgaste y mejorar la fiabilidad. Como se puede ver en la figura 3, permite que toda la EEPROM alcance su índice de resistencia máximo especificado en la hoja de datos. Aun así, hay algunas posibilidades de mejora. El recuento de borrados/escrituras de cada bloque no representa el estado físico real de la memoria, sino un indicador aproximado de la vida útil restante de ese bloque. Esto significa que la aplicación no detectará los fallos que se produzcan antes de que el recuento alcance su valor máximo permitido. La aplicación tampoco puede aprovechar al 100 % la vida útil real de cada bloque de memoria.

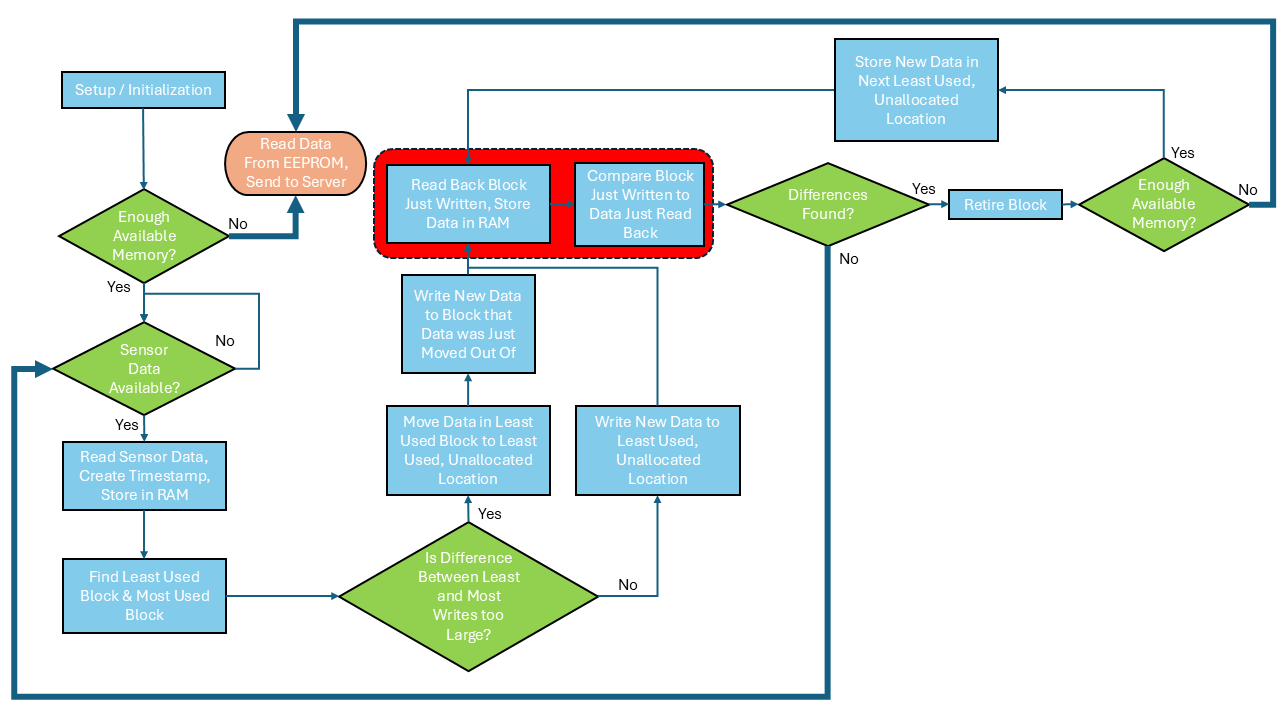

Dado que no hay forma de detectar el desgaste físico, el software necesitará comprobaciones adicionales si se requiere una alta fiabilidad. Un método consiste en volver a leer el bloque que se acaba de escribir y compararlo con los datos originales. Esto requiere tiempo en el bus, sobrecarga de la CPU y RAM adicional. Para detectar fallos tempranos, esta relectura debe realizarse después de cada escritura, al menos durante un tiempo después de que comience la vida útil de la aplicación. Las relecturas para detectar fallos por desgaste de las celdas deben realizarse después de cada escritura, una vez que el número de escrituras se acerque a la especificación de resistencia. Cada vez que no se realice una relectura, el usuario no podrá detectar ningún desgaste y, por lo tanto, se podrán utilizar datos corruptos. El siguiente diagrama de flujo de software ilustra un ejemplo de nivelación de desgaste estática, incluyendo la relectura y la comparación necesarias para garantizar una alta fiabilidad.

Figura 4. Diagrama de flujo de software que ilustra la nivelación de desgaste estática, incluyendo relecturas y comparaciones de la memoria para garantizar una alta fiabilidad

La necesidad de volver a leer y comparar la memoria después de cada escritura puede crear graves limitaciones en el rendimiento y el uso de los recursos del sistema. Existen algunas soluciones para esto en el mercado. Por ejemplo, algunas EEPROM incluyen corrección de errores, que normalmente puede corregir un solo error de bit de cada número especificado de bytes (por ejemplo, 4 bytes). Existen diferentes esquemas de corrección de errores utilizados en la memoria embebida, siendo los más comunes los códigos Hamming. La corrección de errores funciona incluyendo bits adicionales llamados bits de paridad, que se calculan a partir de los datos almacenados en la memoria. Cuando se leen los datos, el circuito interno vuelve a calcular los bits de paridad y los compara con los bits de paridad que se almacenaron. Si hay una discrepancia, esto indica que se ha producido un error. El patrón de la discrepancia de paridad se puede utilizar para localizar con precisión la ubicación exacta del error. A continuación, el sistema puede corregir automáticamente este error de un solo bit invirtiendo su valor, restaurando así la integridad de los datos. Esto ayuda a prolongar la vida útil de un bloque de memoria. Sin embargo, muchas EEPROM no indican que se haya realizado esta operación de corrección. Por lo tanto, sigue sin resolverse el problema de detectar un fallo antes de que se pierdan los datos.

Solución

Para detectar el desgaste físico real, algunas EEPROM incluyen un indicador de bits que se puede leer cuando se detecta y corrige un error de un solo bit en un bloque. Esto permite volver a leer y comprobar un único registro de estado para ver si se ha invocado el ECC durante la última operación. De este modo, se reduce la necesidad de volver a leer bloques de memoria completos para comprobar los resultados. Cuando se determina que se ha producido un error dentro del bloque, se puede suponer que el bloque está degradado y ya no se puede utilizar, por lo que se puede retirar. Gracias a ello, se puede confiar en la información basada en datos para saber cuándo la memoria está realmente desgastada, en lugar de confiar en un contador ciego. Esto elimina esencialmente la necesidad de estimar la vida útil prevista de la memoria en los diseños. Esto es ideal para sistemas que experimentan grandes cambios en su entorno a lo largo de la vida útil de la aplicación final, como las variaciones drásticas de temperatura y voltaje que son comunes en las industrias de fabricación, automoción y servicios públicos. Ahora puede prolongar la vida útil de las celdas de memoria hasta su fallo real, lo que le permite utilizar el dispositivo incluso más tiempo que la especificación de resistencia de la hoja de datos.

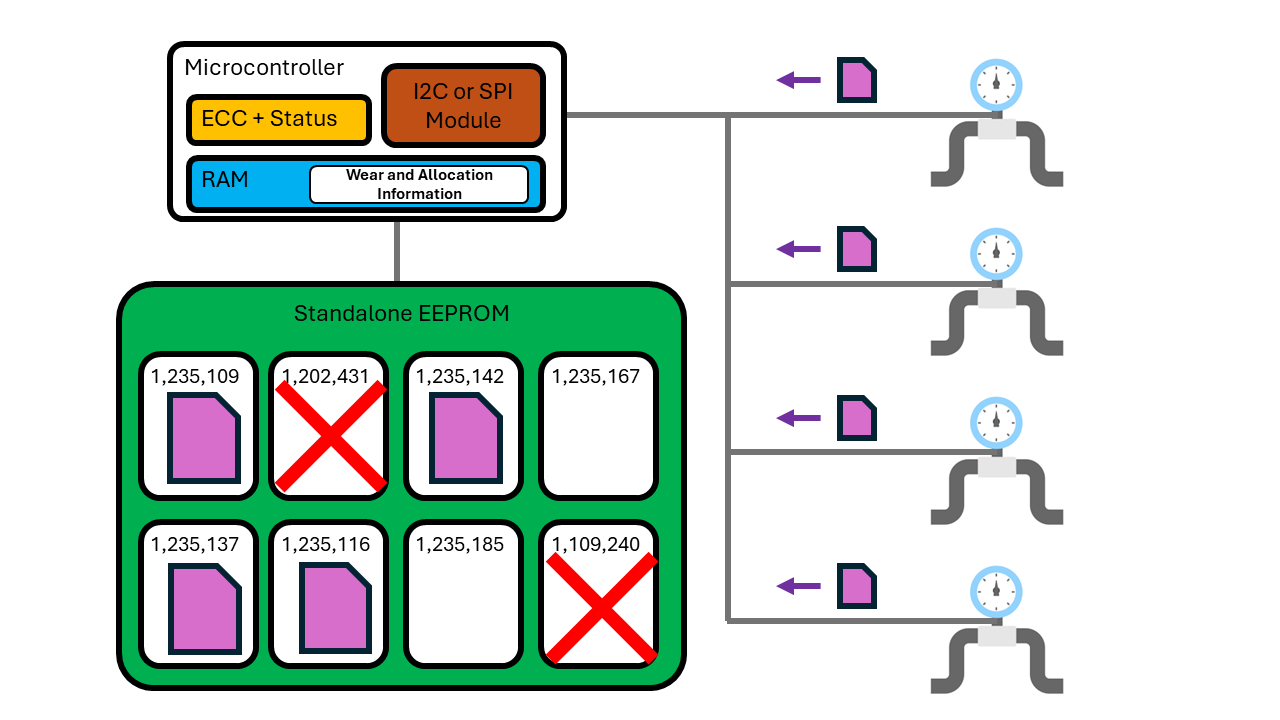

Figura 5. La nivelación del desgaste con una EEPROM con ECC y bit de estado permite maximizar la vida útil de la memoria al hacer funcionar las celdas hasta que fallan, lo que puede aumentar la vida útil más allá de la especificación de resistencia de la hoja de datos.

Microchip Technology, fabricante de semiconductores con más de 30 años de experiencia en la producción de EEPROM, ofrece ahora múltiples dispositivos que proporcionan un indicador para avisar al usuario cuando se ha producido una corrección de errores, lo que a su vez alerta a la aplicación de que debe retirarse un bloque de memoria concreto.

-

-

- I2C EEPROMs: 24CSM01 (1 Mbit), 24CS512 (512 Kbit), 24CS256 (256 Kbit)

- SPI EEPROMs: 25CSM04 (4 Mbit), 25CS640 (64 Kbit)

-

Se trata de un enfoque de nivelación del desgaste basado en datos que puede prolongar aún más la vida útil de la memoria más allá de lo que puede ofrecer la nivelación del desgaste estándar. También es más fiable que la nivelación del desgaste clásica, ya que utiliza datos reales en lugar de recuentos arbitrarios: si un bloque dura más que otro, se puede seguir utilizando ese bloque hasta que la celda se desgaste. Esto puede reducir el tiempo empleado en el bus, la sobrecarga de la CPU y la RAM necesaria, lo que a su vez puede reducir el consumo de energía y el rendimiento general del sistema. El flujo del software se puede actualizar para adaptarse a este nuevo indicador de estado.

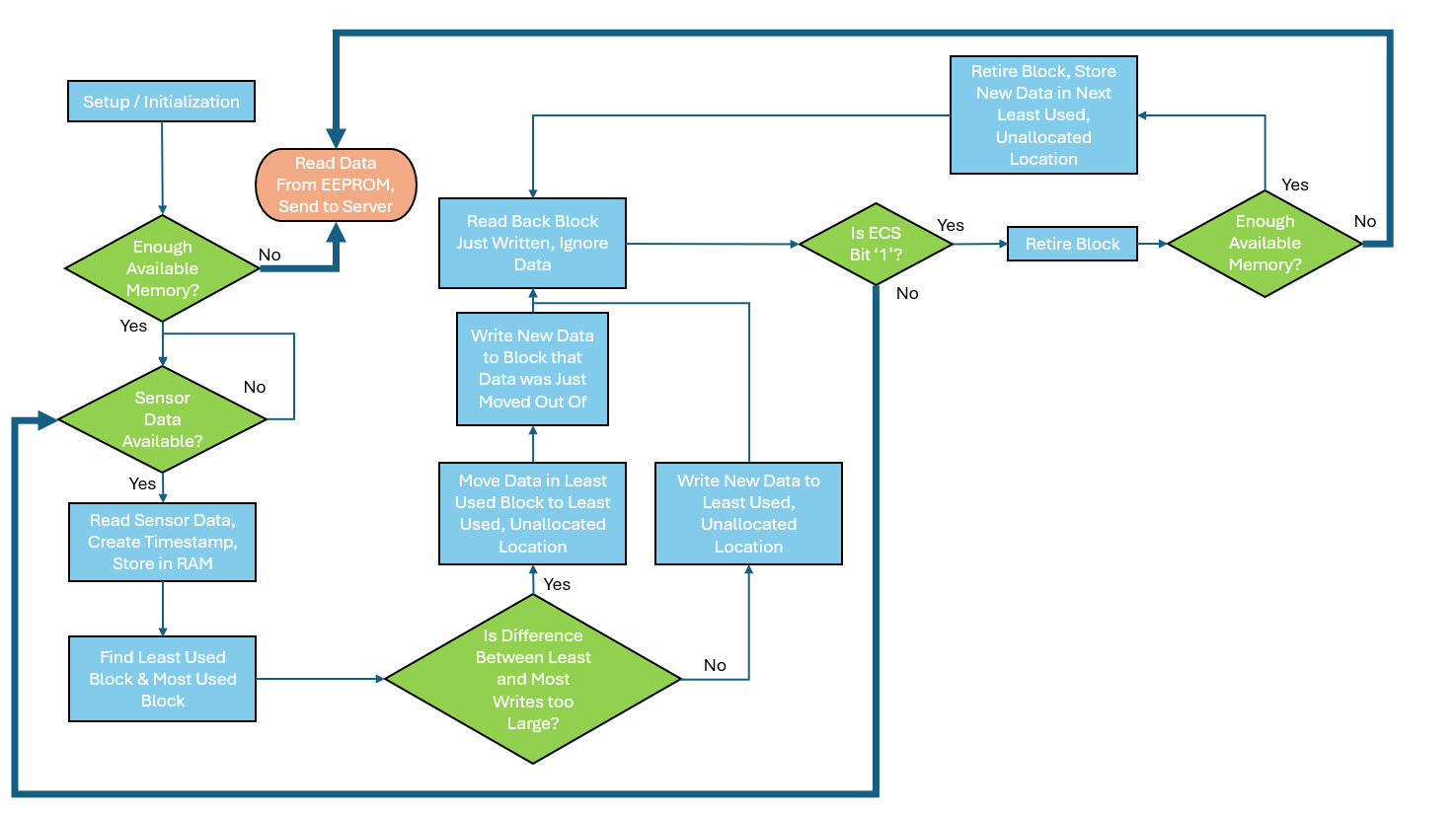

Figura 6. Diagrama de flujo del software que ilustra una rutina simplificada de nivelación de desgaste estático utilizando un indicador de estado de corrección de errores

Como se ilustra en el diagrama de flujo, el uso de un bit de estado de corrección de errores eliminó la necesidad de releer los datos, almacenarlos en la RAM y realizar una comparación completa con los datos recién escritos, lo que liberó recursos y creó un flujo de software conceptualmente más sencillo. Sigue siendo necesaria una relectura de los datos (ya que el bit de estado solo se evalúa en las lecturas), pero los datos pueden ignorarse y descartarse antes de leer simplemente el bit de estado, lo que elimina la necesidad de RAM adicional y la sobrecarga de la CPU por la comparación. El número de veces que el software comprueba el bit de estado variará en función del tamaño de los bloques definidos, que a su vez depende del tamaño mínimo de los archivos que maneja el software.

Ventajas del bit ECS

- Maximiza la vida útil de los bloques EEPROM al ejecutar las celdas hasta que fallan

- Opción de eliminar las lecturas de bloques completos para comprobar si hay datos corruptos, lo que libera tiempo en el bus de comunicación

- Si la nivelación del desgaste no es necesaria o resulta demasiado pesada para la aplicación, el bit ECS sirve como una comprobación rápida del estado de la memoria, lo que facilita la prolongación de la vida útil de los bloques EEPROM y ayuda a evitar el seguimiento de los ciclos de borrado/escritura

La corrección de errores implementada con un indicador de estado es una potente herramienta para mejorar la fiabilidad y prolongar la vida útil del dispositivo, especialmente cuando se utiliza en un esquema de nivelación de desgaste. Cualquier mejora en la fiabilidad es muy deseable en aplicaciones de seguridad funcional, como las automovilísticas y médicas, y es bienvenida por cualquier diseñador que busque crear el mejor sistema posible para su aplicación.