Autor: Justin Sears, Director de Marketing de Producto, SaaS, Altium

La escasez de memoria es real

El auge de la IA —desde altavoces inteligentes y wearables hasta vehículos autónomos y modelos a escala de la nube— está ejerciendo una presión sin precedentes sobre el diseño de hardware electrónico. Si bien las GPU y los aceleradores suelen acaparar la atención, la memoria se está convirtiendo rápidamente en el cuello de botella que define a los sistemas de IA en todos los niveles de la pila.

Las cargas de trabajo de IA dependen de una memoria de alta densidad y acceso rápido para alimentar modelos con un alto consumo de datos. Ya sea que se esté entrenando un modelo generativo en un centro de datos o ejecutando la detección de objetos en un dispositivo edge, el ancho de banda y la capacidad de la memoria ahora actúan como factores determinantes para el rendimiento del sistema, la eficiencia energética y la estabilidad térmica.

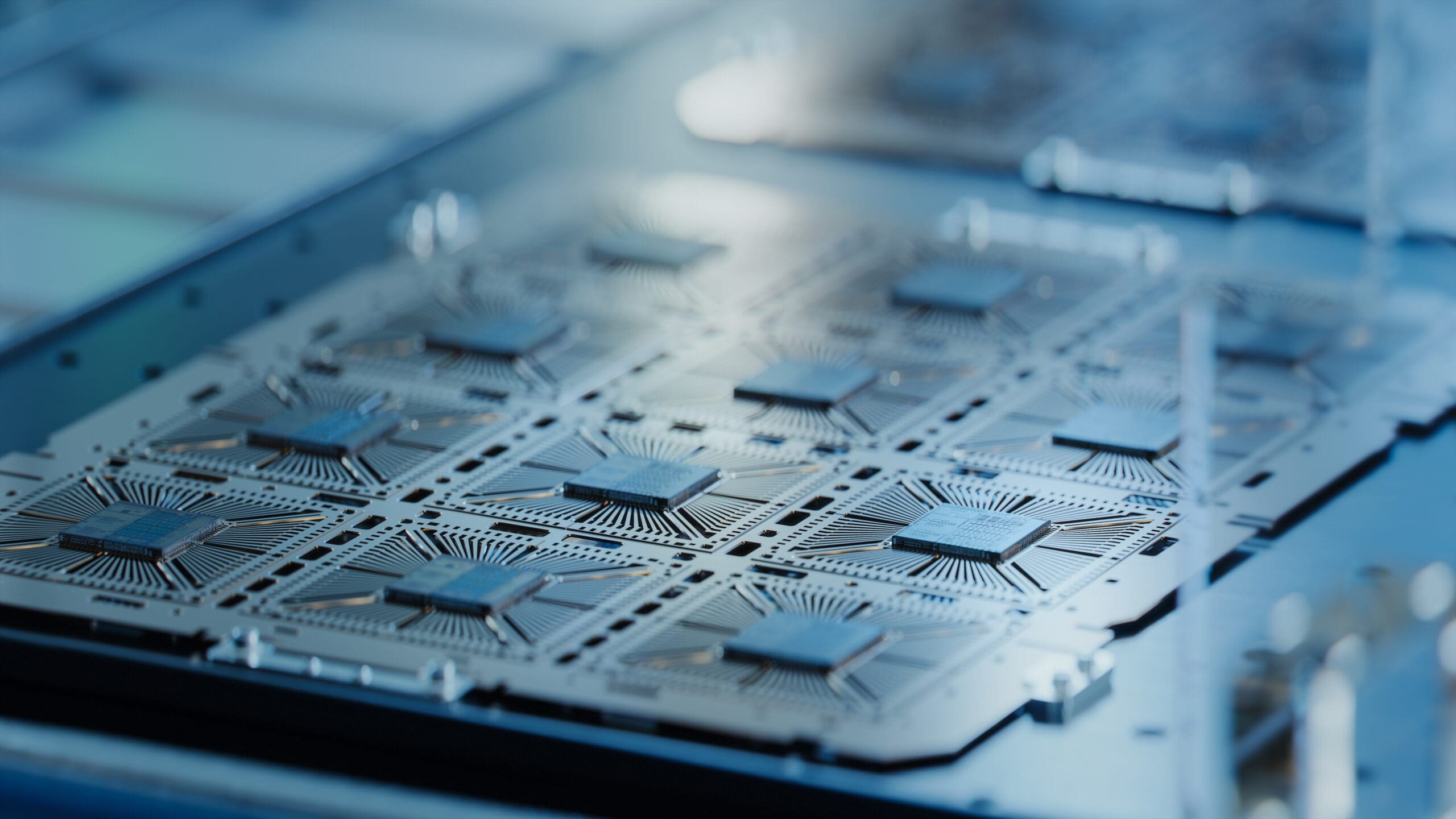

Para satisfacer estas demandas, los equipos de hardware están recurriendo a diversas opciones de arquitecturas de memoria. Estas incluyen memoria de alto ancho de banda (HBM) para una amplia gama de E/S y rendimiento en el entrenamiento de IA, GDDR6/GDDR7 para tareas con alto contenido gráfico o de inferencia, LPDDR5/LPDDR5X para dispositivos de IA Edge con limitaciones energéticas, DRAM apilada en 3D para ofrecer mayor capacidad en espacios más pequeños, y opciones emergentes no volátiles como MRAM y ReRAM para el estado persistente de la IA y la optimización del arranque Edge. Cada una de estas tecnologías introduce restricciones únicas en cuanto a potencia, compatibilidad, diseño térmico y disponibilidad, lo que obliga a realizar concesiones en el diseño a nivel de sistema.

El diseño ahora se define por la memoria

En los flujos de trabajo tradicionales de desarrollo de hardware, la selección de la memoria se realizaba después de decidir entre la CPU o la GPU. En la era de la IA, ese orden se ha invertido. Los diseñadores de hardware actuales están descubriendo que la selección de la memoria impulsa toda la pila de hardware, influyendo en el diseño, la estrategia energética y el factor de forma del producto. Por ejemplo, seleccionar GDDR6 de alta velocidad puede permitir una inferencia más rápida, pero requiere rieles de alimentación dedicados y un enrutamiento de PCB más complejo, lo que añade desafíos térmicos y de EMI. Elegir LPDDR5 para dispositivos móviles alimentados por batería ayuda a ahorrar energía, pero limita el ancho de banda y puede restringir el tamaño del modelo o las velocidades de inferencia. El uso de HBM permite un rendimiento masivo, pero exige innovaciones avanzadas de empaquetado y refrigeración, como cámaras de vapor o sistemas de líquidos, lo cual incrementa el costo.

Estas no son preocupaciones teóricas. Debido a la rápida evolución de las necesidades de memoria de IA, los diseñadores deben definir las huellas de memoria y las interfaces con antelación, a menudo antes de que los modelos de software y firmware sean estables. Esto aumenta el riesgo de tomar decisiones de diseño en las primeras etapas. Una elección de memoria errónea podría requerir reescrituras de la placa base o limitar futuras rutas de actualización.

Volatilidad en la cadena de suministro de memoria

A medida que crece la adopción de modelos de IA, también lo hace la demanda de memoria avanzada. Desafortunadamente, la memoria, en particular la DRAM y la NAND, ha sido durante mucho tiempo un mercado cíclico y sensible a los precios, y el aumento actual de la demanda de IA está agravando dicha volatilidad.

HBM, GDDR6 y LPDDR5 se consideran ahora activos estratégicos. Su producción se concentra en Corea del Sur, que domina el mercado de las memorias DRAM; Taiwán, para servicios avanzados de encapsulado; y Japón, para materiales y memoria especializada.

Esta concentración geográfica conlleva ciertos riesgos, como la inestabilidad geopolítica (por ejemplo, las tensiones en el Estrecho de Taiwán); controles de exportación y restricciones comerciales; Cuellos de botella en la fabricación, ya que la litografía EUV y los equipos específicos para la fabricación de memorias DRAM se limitan a unas pocas fábricas; y la escasez de materiales (p. ej., gases fluorados, fotorresistencias especiales) puede afectar el suministro y retrasar la entrega.

Para los diseñadores que trabajan en la introducción de nuevos productos basados en IA, esto implica plazos de entrega más largos y una mayor exposición a la obsolescencia de los componentes si cambian las hojas de ruta de la memoria o si una pieza determinada escasea.

No se trata solo de cantidad, sino de acceso

En el hardware IA, una mayor cantidad de memoria solo es útil si es del tipo correcto, está en el lugar correcto y está conectada correctamente.

La transición de la computación de propósito general a cargas de trabajo centradas en IA permite a los equipos de desarrollo de productos considerar nuevos enfoques de diseño. La memoria estrechamente acoplada, por ejemplo, reduce la latencia, pero requiere una mayor integración con los procesadores o SoC. La memoria débilmente acoplada ofrece flexibilidad, pero puede introducir cuellos de botella según la arquitectura. Los patrones de acceso a la memoria, como la reutilización de tensores, el acceso por pasos o la escasez, deben optimizarse en función de la estructura del modelo y la secuencia de cálculo. Las decisiones de particionamiento, como el almacenamiento de pesos en HBM, las activaciones en LPDDR y los datos intermedios en NVM, pueden afectar drásticamente el rendimiento, los perfiles térmicos y la duración de la batería.

La compatibilidad es un campo minado a nivel técnico. Los ingenieros deben validar que la memoria no solo sea eléctricamente compatible con chips de IA, FPGAs o SoCs, sino que también se ajuste lógicamente en cuanto a ancho de banda, latencia y paralelismo. Una discrepancia en este aspecto puede reducir el rendimiento computacional, inflar los presupuestos de energía o provocar la infrautilización de costosos aceleradores de hardware.

La planificación de memoria con visión de futuro es ahora una ventaja competitiva

Las empresas que lanzan hardware IA con éxito hoy en día no solo optimizan el rendimiento, sino que incorporan resiliencia en su estrategia de memoria desde el principio.

Esto implica considerar el riesgo de abastecimiento y el estado del ciclo de vida durante la selección de la memoria, simular el acceso a la memoria y el rendimiento en las primeras etapas del diseño, colaborar con los equipos de hardware, software y cadena de suministro para anticipar los obstáculos e invertir en plataformas de diseño que admitan la colaboración en tiempo real y la inteligencia de componentes.

Cuando los equipos de diseño y abastecimiento operan de forma aislada, las decisiones sobre la memoria pueden retrasarse o tomarse de forma aislada, lo que resulta en errores costosos y la pérdida de oportunidades de mercado. Pero cuando los equipos trabajan juntos desde el principio, pueden identificar alternativas, minimizar los riesgos de disponibilidad y diseñar sistemas que equilibren la potencia, el rendimiento y la seguridad de la cadena de suministro.

A medida que los diseñadores avanzan hacia la integración de la IA en todo, desde los sensores Edge hasta la infraestructura del centro de datos, la memoria se está convirtiendo en el nuevo campo de batalla, donde compiten las estrategias de rendimiento, escalabilidad y disponibilidad de componentes. Los diseñadores que tratan la memoria no como una ocurrencia de último momento sino como una limitación central serán los que logren llevar sus productos al mercado, satisfagan las necesidades de las cambiantes cargas de trabajo de IA y superen a los competidores en la carrera por crear los próximos grandes productos.