Directrices para diseño de hardware y explicaciones complementarias para quienes diseñen un sistema que utilice ULPI (UTMI+ low pin interface).

La aplicación más habitual del interface ULPI (UTMI+ low pin interface) consiste en sistemas que conecten un transceptor USB 2.0 de alta velocidad a un enlace. Este artículo tiene como objetivo proporcionar una guía de diseño y verificación para quienes diseñen un sistema que utilice ULPI con directrices de diseño de hardware, así como explicaciones complementarias sobre el protocolo ULPI.

USB es un interface de datos serie permite el intercambio de datos entre un ordenador principal (host) y un dispositivo. ULPI define un interface entre el enlace y el transceptor USB para establecer una conexión o enlace entre el transceptor y el motor de interface serie (Serial Interface Engine, SIE) con tan solo 12 patillas.

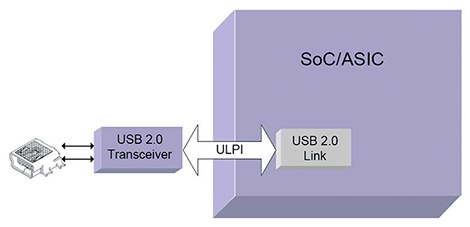

ULPI es un interface basado en estándares que proporciona una conexión punto a punto de alta capacidad entre un SoC o ASIC y un transceptor USB de alta velocidad, tal como muestra la Fig. 1. ULPI es una versión con menos patillas y una extensión del interface UTMI (USB transceiver macrocell interface) y la especificación UTMI+. La Fig. 2 muestra un ejemplo de interconexión del sistema.

Diseño del hardware

Para cumplir la especificación de sincronización de ULPI y asegurar un diseño robusto del interface ULPI existen tres elementos fundamentales del sistema que ayudan a conocer las necesidades de sincronización de ULPI: el transceptor USB, el diseño de placa de circuito impreso y el SoC.

La hoja de datos de cada transceptor USB ULPI de SMSC, filial de Microchip Technology, detalla su sincronización de interface. Para todos los productos de SMSC, la sincronización a ULPI del transceptor alcanza o supera los requisitos definidos en la especificación ULPI.

La placa de circuito impreso debería basarse en las directrices de diseño de SoC proporcionadas por el proveedor de SoC. Los principales aspectos a tener en cuenta para la placa en todos los diseños de ULPI son las pistas de impedancia controlada (50 a 60Ω), la longitud de la pista y la influencia entre pistas. Una regla conservadora para la longitud de la pista con ULPI consiste en limitar cada pista hasta una longitud total inferior a 7,6 cm, pero este parámetro depende totalmente del SoC utilizado. Incluso SoC de un mismo proveedor que utilicen el mismo IP de conexión están sujetos a diferencias como el enrutado y la multiplexación de patillas, que afectan a la sincronización de ULPI.

La señal CLK es la referencia de reloj para todas las señales ULPI y lógicas. Lo ideal sería que las pistas de ULPI se enrutarán a menos de 1,3 cm de CLKOUT.

Para aumentar la confianza en el diseño de la placa del ULPI, se debería realizar el análisis de integridad de señal con el objetivo de incrementar la calidad de señal. Una simulación precisa puede poner de manifiesto los problemas de integridad de señal en una fase temprana del ciclo de diseño, además de reducir el tiempo de desarrollo y el coste.

Una resistencia de terminación en serie colocada cerca de la fuente de reloj puede resultar beneficiosa en algunas aplicaciones de ULPI, pero esto se confirma mejor mediante simulación. Si es posible, se recomienda que los diseños incluyan al menos una resistencia de terminación serie de la fuente de reloj de 0Ω si se llega a la conclusión de que la terminación serie es necesaria una vez montada la placa de circuito impreso.

Al verificar la sincronización o al diagnosticar un problema en un interface USB, a menudo un analizador lógico puede realizar estas tareas con rapidez. Para hacerlo más fácil se recomienda llevar todas las señales ULPI a un punto de prueba. Lo ideal sería llevar las señales a un interface de sonda de analizador lógico de baja capacidad Tektronix

D-Max o Agilent Soft Touch. Sin embargo, para la mayoría de las aplicaciones lo más práctico sería que sencillamente se pudiera acceder a todas las señales ULPI a través de un punto de prueba o de una vía accesible desde la parte superior o inferior de la placa de circuito impreso.

Al igual que todos los circuitos digitales de alta velocidad, los diseños robustos deberían aislar las señales ULPI frente al ruido de las señales adyacentes y las fuentes de alimentación.

Arranque y reinicios

La Fig. 3 muestra la secuencia de arranque del transceptor de SMSC desde el momento en que la fuente de alimentación de E/S de ULPI es estable (T0) hasta el momento en que el transceptor completa su POR (T2). Cuando se reinicia el transceptor USB, la patilla DIR pasa a estado alto hasta que el reloj de salida de 60 MHz sea estable. En modo de reloj de entrada de ULPI, DIR permanecerá en estado alto hasta que el PLL interno esté fijado y sea estable. En cuanto el transceptor y el enlace acaban su reinicio el transceptor envía un RXCMD al enlace.

RESETB indica una entrada de reinicio de hardware activo en estado bajo en el transceptor USB. La confirmación de RESETB hará que se detenga el reloj de salida de 60 MHz y DIR pase a estado alto. Internamente, el transceptor USB saldrá de un reinicio por hardware de la misma manera que saldría de un POR, como muestra la Fig. 3. El PLL se volverá a fijar y los registros ULPI vuelven a sus estados por defecto.

El transceptor USB se puede reiniciar configurando cinco bit del registro de control de función. Mientras el transceptor USB se reinicia, DIR pasará a estado alto. Dado que el reloj de 60 MHz procedente del PLL permanece fijo durante el reinicio, el reloj de salida de 60 MHz (CLKOUT) seguirá en funcionamiento.

Sincronización y protocolo

La especificación ULPI define el modo síncrono, el modo asíncrono de bajo consumo y otros modos asíncronos opcionales. Si bien los transceptores USB de SMSC soportan todos los modos asíncronos definidos por la especificación, este artículo se centra en el modo síncrono.

El interface ULPI síncrono toma como referencia un reloj de 60 MHz que puede alimentarse mediante el transceptor USB o el SoC. Todos los transceptores ULPI deben ser capaces de proporcionar un reloj de salida de 60 MHz y de manera opcional pueden aceptar un reloj externo de 60 MHz. Los últimos modelos de transceptor USB de SMSC pueden trabajar en modos de reloj de salida y entrada de 60 MHz tal como define la especificación.

Todas las señales de datos y control de ULPI toman como referencia el flanco ascendente de un reloj de referencia de 60 MHz. La Fig. 4 está tomada de la especificación ULPI y muestra el diagrama de tiempos para el funcionamiento de ULPI síncrono.

La especificación ULPI exige el soporte al modo de reloj de salida y es el modo de reloj ULPI más habitual. En este modo, el transceptor USB genera el reloj de ULPI de 60 MHz utilizado por el enlace. Los transceptores USB de SMSC también se pueden utilizar en su mayoría con una fuente de reloj de 60 MHz. Cuando se utiliza el modo de reloj de entrada, el enlace debe suministrar el reloj ULPI de 60 MHz al transceptor USB. A diferencia de algunos proveedores de transceptores USB que anuncian su soporte a este modo, SMSC cumple íntegramente los parámetros de sincronización exigidos por la especificación ULPI.

Además de enviar transmisiones y recibir datos a través del bus de datos, ULPI define un byte de comando de transmisión generado por el enlace y un byte de comando de recepción generado por el transceptor. Un comando procedente del enlace inicia una transferencia ULPI desde el enlace al transceptor USB. El byte TX CMD informa al transceptor sobre el tipo de transacción iniciado por el enlace. El enlace inicia una escritura en un registro inmediato en el transceptor, enviando para ello primero el byte TX CMD; de forma parecida, inicia la lectura de un registro inmediato enviando en primer lugar el byte TX CMD.

Se enviará un RXCMD cuando el USB reciba información (LineState, RxActive, RxError) o cuando se produzca un evento de interrupción (Hostdisconnect, Vbus, IdGnd, interrupciones Carkit, convertidor RID finalizado). Un RXCMD tiene una prioridad más baja que los datos recibidos y transmitidos por USB, pero su prioridad es más alta que los comandos de lectura y escritura de registro.

Un TX CMD procedente del enlace inicia una transferencia ULPI del enlace al transceptor USB. El transceptor logra controlar el bus de datos ya que recibe un paquete al confirmar DIR cuando está recibiendo datos.

Una suspensión de ULPI no es lo mismo que una suspensión de USB. La suspensión de ULPI se define en la especificación ULPI y proporciona un modo de bajo consumo para el transceptor USB. Para entrar en modo de suspensión, se debe borrar el bit SuspendM en el registro de control de función. El transceptor USB no se puede despertar desde la suspensión; el enlace debe confirmar STP para despertar al transceptor USB.

Como alternativa, el transceptor USB puede despertarse al recibir un reinicio por hardware.

Diseño del software

Dado que los interfaces ULPI y USB del transceptor USB se basan en estándares, se puede utilizar un driver común para cualquier transceptor USB que cumpla la especificación ULPI. Esto se suministra habitualmente con el paquete de soporte de la placa (Board Support Package, BSP) del proveedor de SoC.

Los registros utilizados para el funcionamiento del USB se detallan en la especificación ULPI. Los drivers de software deberían escribirse para utilizar únicamente los registros estándar. Esto permite mantener la compatibilidad de software con los transceptores ULPI de diferentes fabricantes. El transceptor de SMSC se puede diseñar añadiendo pocos cambios o incluso ninguno al software existente.

La especificación ULPI proporciona registros específicos del proveedor para características exclusivas del propio proveedor o del producto. Por ejemplo, los transceptores USB de SMSC ofrecen características que aumentan la velocidad de transmisión y la sensibilidad de recepción que se configuran mediante estos registros específicos de proveedor.

Conclusión

Este artículo ha ofrecido algunas directrices de diseño del hardware y explicaciones para ayudar a diseñar un sistema utilizando un ULPI.