Los fabricantes de equipamiento original u OEM (Original Equipment Manufacturers) están interesados en desarrollar un hardware seguro que afronte un conjunto de amenazas de seguridad como el robo y la corrupción de datos, la apropiación de equipos, el clonado y el robo de diseños. Además, las amenazas de seguridad ya no se limitan a sistemas en uso activo. Los atacantes se marcan como objetivo componentes que se encuentren en cualquier punto de la vida útil del producto, desde el inicio de su fabricación y su envío al fabricante subcontratado hasta la integración en el sistema y a lo largo de toda su vida operativa.

Por tanto, los OEM necesitan una solución de seguridad robusta que proteja el hardware frente a estas amenazas en cada fase de la vida útil del sistema. ¿Cómo pueden abordar este problema los OEM? Deben establecer uno o más dispositivos como raíz de confianza (root-of-trust, RoT) de hardware para utilizarlos como plataforma que proporcione capacidades criptográficas con el fin de proteger sus sistemas.

Entre dichas capacidades se encuentran la criptografía de datos, la autenticación de datos, la autenticación del firmware, la autenticación del sistema y la criptografía de código/ configuración. Un dispositivo RoT es el primer eslabón en una cadena de confianza que protege todo el sistema. Una vez que los diseñadores hayan identificado el primer dispositivo de confianza (generalmente un PLD, FPGA o microcontrolador), puede servir como base que aporte las funciones criptográficas necesarias para proteger el hardware del sistema.

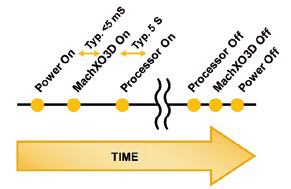

Los dispositivos RoT deben contener el hardware necesario para verificar su propia configuración y deberían ser los primeros dispositivos digitales en arrancar al conectar la alimentación y los últimos en apagarse al desconectar la alimentación. ¿Qué tipo de arquitectura de seguridad necesitan los diseñadores de sistemas ante el constante aumento del número y la sofisticación de las amenazas? En primer lugar y por encima de todo, toda solución debe ser lo suficientemente robusta como para ofrecer protección frente a amenazas nuevas y ya existentes para el firmware. Con el objetivo de ayudar a los diseñadores a medir la capacidad de su solución, el NIST (National Institute of Standards and Technology) ha definido recientemente un nuevo mecanismo de seguridad uniforme. Las directrices NIST SP 800 193 PFR (Platform Firmware Resilience) han sido diseñadas con el fin de garantizar de forma integral que se ha establecido una RoT para todo el firmware del sistema. Los desarrolladores de la nueva especificación se han guiado por tres directrices:

- Protección: proteger la memoria de firmware no volátil mediante control de acceso

- Detección: detecta y evita gracias a la criptografía la ejecución de código malicioso

- Restauración: en caso de corrupción, se restaura el sistema al último firmware de confianza

Opciones para el motor

Un motor ideal que proporcione seguridad de hardware se caracterizaría por su bajo consumo, alto grado de flexibilidad de diseño, escalabilidad y ocupación de poco espacio. Los microcontroladores ofrecen excelentes recursos de computación pero no suelen incorporar el conjunto de capacidades necesarias para ayudar a activar otros procesadores o componentes del sistema. Además, cuando un microcontrolador está en funcionamiento también le resulta difícil supervisar su propia memoria de arranque. Las FPGA (Field Programmable Gate Arrays (FPGA) ofrecen una importante ventaja respecto a los microcontroladores. A menudo se emplea una FPGA como el primer dispositivo en activarse y coordinar el arranque del sistema y el último dispositivo en apagarse tras coordinar el apagado del propio sistema. Esto hace que sea ideal simplemente para establecer una RoT. Los diseñadores pueden aprovechar la naturaleza paralela de las FPGA para comprobar varias memorias en paralelo y mejorar así significativamente el tiempo de arranque. Además, a diferencia de los microcontroladores, las FPGA pueden proteger el almacenamiento no volátil ya que proporcionan supervisión en tiempo real. Por último, aportan la lógica y las interfaces que se necesitan para permitir la recuperación del firmware en caso de corrupción del sistema.

MachXO3D de Lattice: la FPGA raíz de confianza para una seguridad integral de hardware

Lattice ha anunciado recientemente la FPGA MachXO3D para cubrir la creciente necesidad de seguridad del firmware en una amplia variedad de aplicaciones. Se trata de la primera FPGA de pequeño tamaño y bajo consumo dirigida a aplicaciones de control del sistema diseñada para proteger el firmware del sistema en numerosas aplicaciones, entre ellas computación, comunicaciones, control industrial y automoción. Este nuevo dispositivo ayuda a los OEM a protegerse frente a robos de datos, modificación de datos, robos de diseños, clonado de productos, superposición, manipulación y apropiación de dispositivos simplificando la implementación de un sistema de seguridad de hardware integral, flexible y robusto a lo largo de la vida útil del producto. La MachXO3D, cuyas patillas son compatibles con los conocidos dispositivos MachXO3 de Lattice utilizados en numerosas aplicaciones con PLD de control, se consolida como la línea de PLD de control de Lattice especialmente dirigida a aplicaciones de protección del firmware.

Integración simplificada

La implementación sencilla de la seguridad del firmware ha sido prioritaria en el diseño de la MachXO3D. Los diseñadores de Lattice querían asegurarse de que los desarrolladores pudieran acceder con facilidad a las ventajas del nuevo dispositivo. Dado que más del 50 por ciento de todos los sistemas de comunicaciones y servidores utilizan PLD de control basados en la arquitectura MachXO, el nuevo dispositivo ha sido diseñado expresamente para sus patillas sean compatibles con la arquitectura precedente. Esto permite que los desarrolladores puedan adaptar o añadir fácilmente estas nuevas capacidades de seguridad a sus soluciones de control existentes. Ante la rápida evolución de la demanda de estas nuevas capacidades de seguridad y a la consolidación de la arquitectura XO, no es de sorprender que cinco de los mayores OEM de servidores ya trabajen directamente con Lattice en diseños basados en la MachXO3D. Y dado que los desarrolladores utilizan a menudo un dispositivo MachXO3 como primer componente en encenderse y último en apagarse, pueden construir con rapidez las capacidades de una raíz de confianza y una cadena de confianza sin preocuparse porque algunos de sus dispositivos digitales vayan por delante de su PLD de Lattice. Permite una seguridad flexible y mantiene la integridad del sistema

- La arquitectura MachXO se utiliza para desarrollar la mayoría de PLD de control en infraestructuras críticas • MachXO3 y MachXO3D tienen patillas compatibles

- MachXO3D es el primer dispositivo en encenderse y el último en apagarse en la plataforma para implementar una cadena de confianza fácilmente

- Más de cinco OEM de servidores trabajan en diseños con MachXO3D

Seguridad integral

Lattice ha potenciado la funcionalidad del PLD de control de la FPGA MachXO3D para atender la creciente preocupación por la seguridad del hardware mediante un bloque de seguridad mejorada que proporciona una RoT de hardware y capacidades criptográficas que necesitan los desarrolladores para afrontar diversas amenazas de seguridad.

- Para asegurar la seguridad del diseño y la protección frente a robo de propiedad intelectual (IP), Ma chXO3D incorpora criptografiado de flujo de bits.

- Para proteger la integridad de las fuentes de ingresos del OEM y sus marcas, el dispositivo dispone de una identificación segura del dispositivo que se puede utilizar junto con otras funciones de seguridad para ofrecer autenticación del dispositivo y la plataforma.

- La criptografía de cueva elíptica, las funciones de clave pública y privada y el criptografiado/ descriptografiado AES ofrecen protección frente al robo de datos.

- La autenticación de curva elíptica y la generación de firmas proporcionan los bloques funcionales para la autenticidad del firmware y los datos de aplicación general.

Implementación robusta conforme a NIST

Un indicio del robusto diseño de laMachXO3D es que se trate de la primera FPGA del mercado destinada al control que cumple las directrices NIST SP 800 193 PFR (Platform Firmware Resiliency). Como tal, el dispositivo protege la memoria no volátil mediante control de acceso, detección y prevención criptográfica de arranque y código malicioso, y en caso de corrupción, se restaura el sistema al último firmware de confianza. Además, la MachXO3D puede reconfigurar dinámicamente los puertos de E/S en cualquier momento para minimizar la superficie de ataque el sistema.

Implementación flexible

La flexibilidad de diseño también ha sido una cuestión central. La mayoría de los clientes de Lattice aprecian la capacidad de instalar mejoras del sistema en la arquitectura XO tras instalar el equipo. Esta reprogramabilidad ofrece un control dinámico de la superficie de ataque y permite que los usuarios actualicen fácilmente la FPGA para lograr que los ataques de firmware más recientes queden obsoletos. En consecuencia, los diseñadores de Lattice deseaban ofrecer una capacidad de seguridad robusta sin que ello afectara a la programabilidad. La MachXO3D añade dos funciones clave para cubrir estas exigencias conflictivas. El dispositivo realiza una autenticación del código para confirmar que cada configuración cargada tiene la firma digital apropiada dentro del motor de configuración física. Al mismo tiempo, la MachXO3D integra memoria flash adicional para almacenar dos configuraciones del dispositivo en cualquier momento. Esta capacidad de doble arranque permite que el sistema aplique la configuración de reserva en el dispositivo si se pone en peligro.

Aplicaciones típicas

La MachXO3D está diseñada para atender una amplia variedad de aplicaciones en varios mercados. Entre sus aplicaciones potenciales se encuentran equipos de comunicaciones inalámbricas 5G como conmutadores y enrutadores, servidores y ordenadores corporativos, automatización industrial y dispositivos para IoT industrial. El diagrama de bloques mostrado a continuación muestra una implementación típica de la MachXO3D en un servidor seguro y consta de un controlador (Board Management Controller, BMC), una CPU principal y diversas CPU o FPGA adicionales. Normalmente una pequeña FPGA denominada PLD de control gestiona todos los controles de reinicializaciones y de la fuente de alimentación de la placa. Todos los procesadores arrancan desde una memoria SPI o SPI cuádruple. Los desarrolladores ahora pueden actualizar la seguridad de su servidor utilizando la MachXO3D como una pequeña FPGA y añadiendo un pequeño interruptor. Esta configuración permite el arranque de la propia FPGA, verificar cada memoria SPI y el arranque de dichos componentes (suponiendo que las memorias sean correctas y estén debidamente firmadas). Si las memorias SPI no son correctas, la MachXO3D toma pasos adicionales como as apagar el sistema o intentar reconfigurar desde otra fuente, dependiendo de la preferencia del cliente. Tras el arranque del sistema, la MachXO3 también supervisa el acceso a varias memorias SPI para evitar escrituras no autorizadas.

Seguridad durante toda la vida útil

Teniendo en cuenta la creciente necesidad de una mayor seguridad a lo largo de toda la vida útil del producto, Lattice ha revisado su flujo de integración de prueba del dispositivo en la fabricación para permitir el uso del criptografiado de clave pública para la programación segura de los dispositivos en un entorno inseguro. Esto garantiza que cada dispositivo siga siendo seguro a lo largo de toda su vida útil. La nueva capacidad asegura a los clientes que sus dispositivos sigan siendo seguros desde el momento en que salen de la fábrica de Lattice y hasta el fin de su vida operativa.

Conclusión

Los sistemas digitales se encuentran actualmente más amenazados que nunca. Los piratas informáticos revelan las vulnerabilidades del sistema y las aprovechan para robar datos y diseños, manipular o apropiarse de productos, o crear clones. Estos ataques se realizan a lo largo de toda la vida útil del producto. Solo en 2018, los ataques a firmware inseguro provocaron que miles de millones de circuitos integrados en sistemas de computación, comunicaciones, control industrial y automoción fueran vulnerables a estos riesgos de seguridad. En última instancia, el hardware vulnerable expone a los OEM a sufrir riesgos financieros y una reputación negativa de su marca.

¿Cómo pueden mitigar esta amenaza los diseñadores y proteger sus sistemas? Mediante la implementación de sistemas con una seguridad integral, flexible y robusta basada en técnicas de raíz de confianza y cadena de confianza del hardware. La nueva FPGA MachXO3D de Lattice permite que los diseñadores mejoren la funcionalidad de su control de la seguridad con capacidades de raíz de confianza y doble arranques. Al mismo tiempo, el nuevo dispositivo promete simplificar enormemente la implementación de soluciones de seguridad que cubran toda la vida útil del componente.