Por: Robert Perkel

Al descargar las tareas y acciones del microcontrolador o microprocesador principal, los microcontroladores de tareas específicas ayudan a simplificar el proceso de diseño para una multitud de aplicaciones.

En el mundo actual, los grandes microcontroladores (MCU) de 32 bits y los microprocesadores (MPU) que ejecutan un sistema operativo en tiempo real (RTOS) son cada vez más comunes. Sin embargo, un solo microcontrolador de gran tamaño que gestiona una aplicación compleja puede tener problemas con los recursos de la CPU en lo que respecta a las pequeñas tareas de mantenimiento, que no son complejas, pero que consumen mucho tiempo.

Los dispositivos más pequeños, como los MCU de 8 y 16 bits, pueden utilizarse para descargar estas tareas del dispositivo de 32 bits, lo que impulsa la innovación y el desarrollo en todo el espectro de microcontroladores, desde los de 8 hasta los de 32 bits.

Muchas tareas son más gestionables si el dispositivo de 32 bits descarga algunas de estas tareas a subprocesadores que se encargan de sólo 1 o 2 de estas tareas pero que requieren poca supervisión al hacerlo. Esto libera recursos de la CPU en el procesador principal, lo que reduce la complejidad del software y mejora el rendimiento y el tiempo de ejecución.

Por ejemplo, se puede utilizar un MCU de 8 bits para crear un extensor de E/S. Los extensores de E/S no son dispositivos complejos, pero utilizan mucho tiempo de la CPU debido a la frecuente atención de las interrupciones. Usando un MCU dedicado a esta tarea, el dispositivo más grande puede reducir su utilización de E/S y el número de interrupciones que necesita gestionar. Además, las características del extensor de E/S se establecen en el software, lo que permite personalizarlo y ajustarlo a la aplicación.

La mayor ventaja de crear un extensor de E/S utilizando un MCU de 8 bits es la flexibilidad. El conjunto de características de un ASIC de expansión de E/S está integrado en el dispositivo, mientras que el MCU define su comportamiento basándose en el software que ejecuta. Esta flexibilidad permite que la versión basada en el MCU se adapte a las necesidades de la aplicación final.

Implementación del extensor de E/S Avanzado

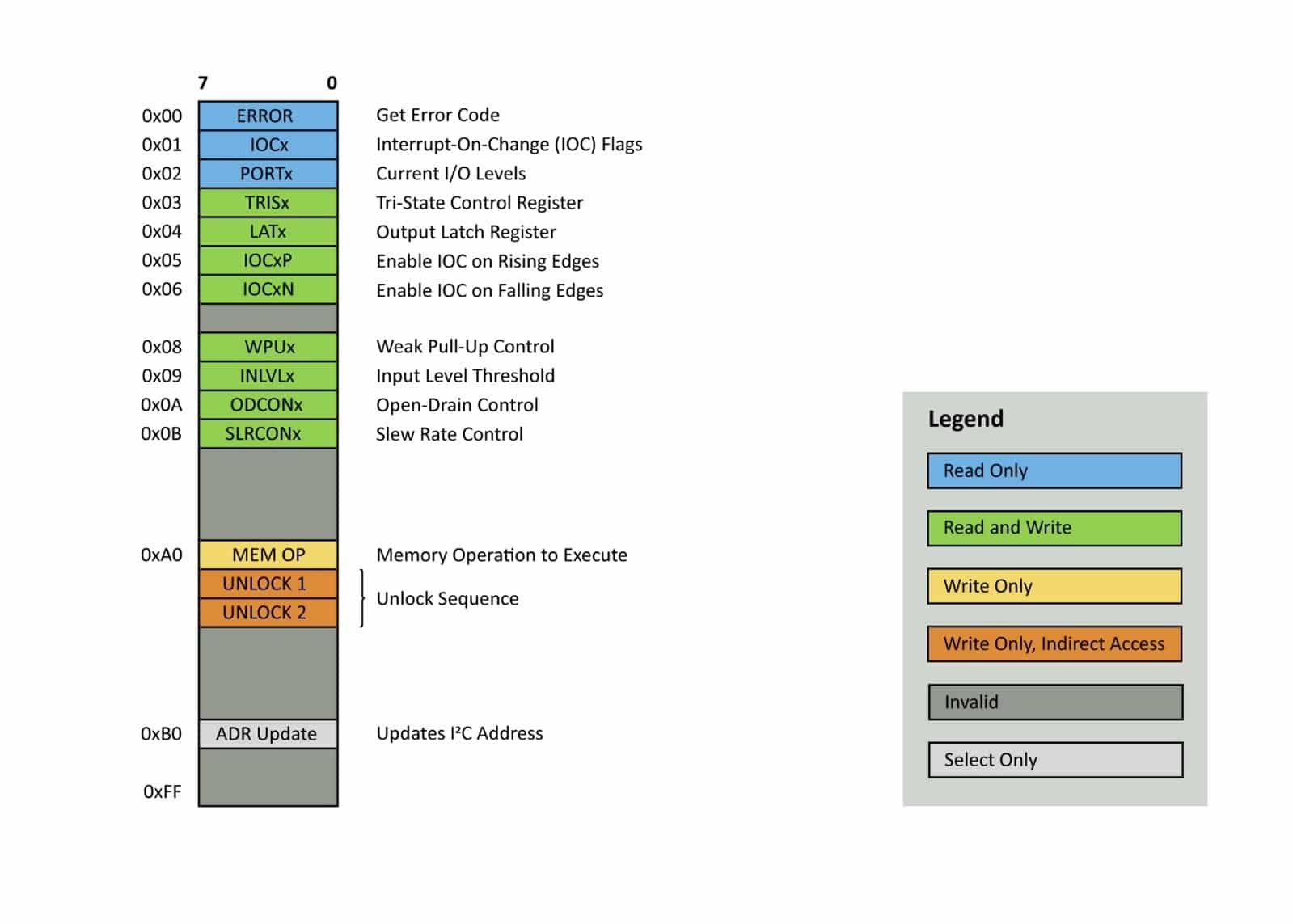

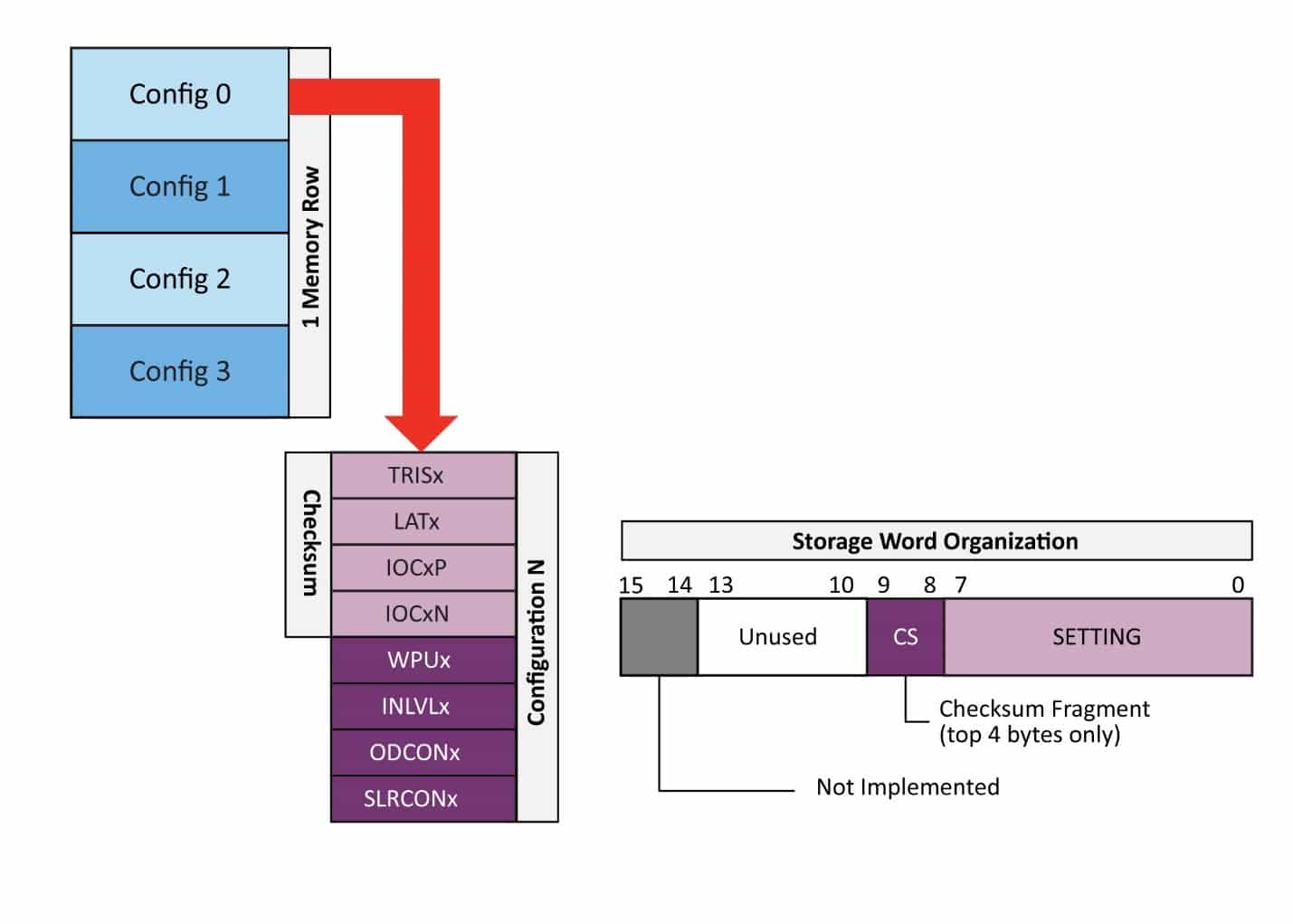

Internamente, el extensor de E/S avanzado opera en una estructura basada en una tabla de búsqueda. Antes de leer o escribir, se envía una dirección virtual. Esta dirección no se correlaciona con los registros del microcontrolador – sólo es específica de la tabla de búsqueda. Esto significa que las características que no están en los registros de hardware del microcontrolador se pueden añadir de forma transparente. Además, las entradas de la tabla pueden reorganizarse fácilmente para usos específicos. Otra ventaja de esta estructura es la posibilidad de añadir permisos a la tabla de búsqueda. Por ejemplo, para crear un registro de sólo lectura, simplemente omita la entrada de la tabla de búsqueda de escritura.

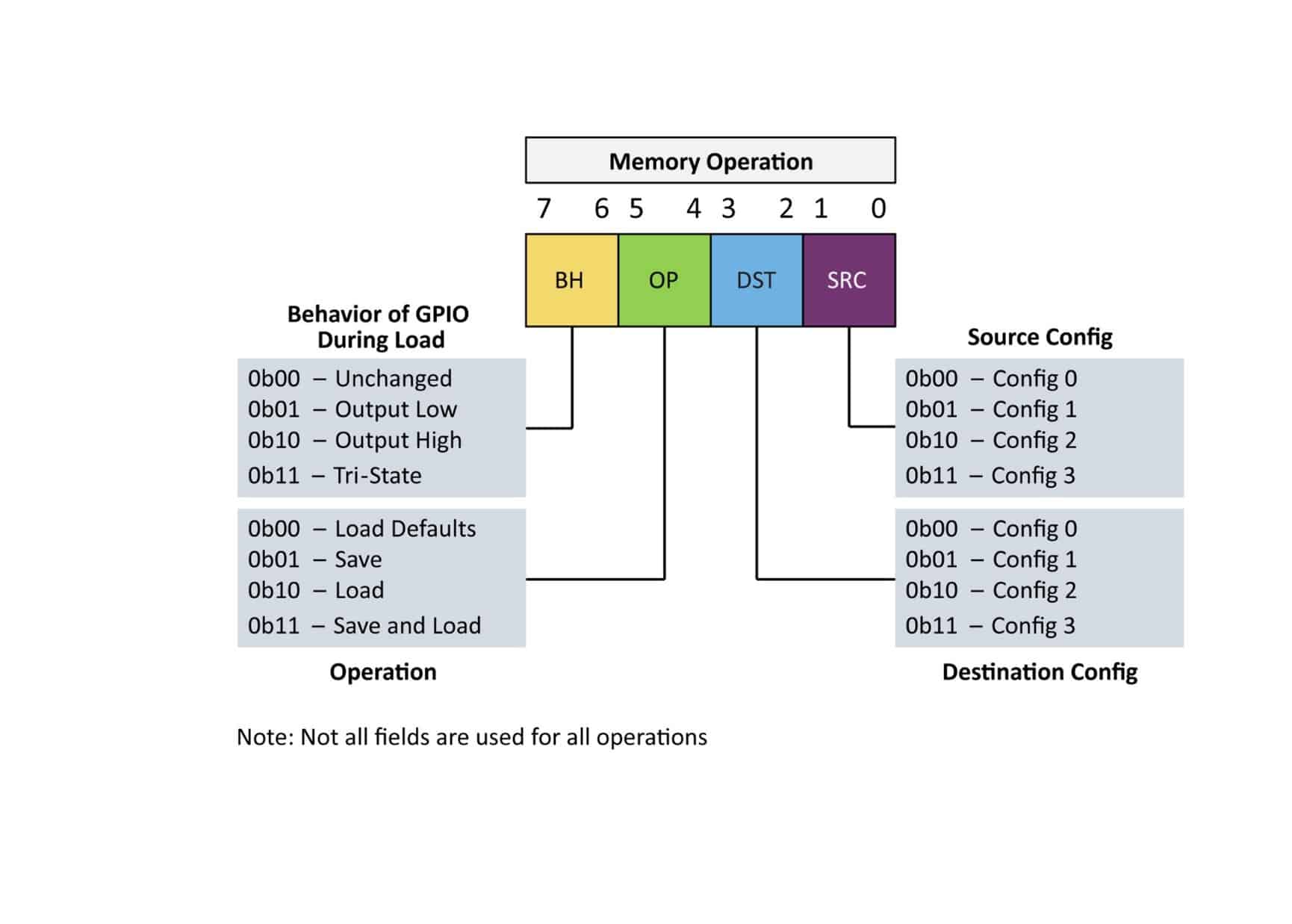

Esta estructura más compleja también se presta a funcionalidades no estándar. La función «MEM OP» permite al MCU guardar o cargar su configuración actual de entradas y salidas de propósito general (GPIO) en la memoria.

MEM OP también puede restablecer la configuración GPIO a los parámetros establecidos al compilar.

Opcionalmente, el microcontrolador puede configurarse para cargar la configuración guardada al encenderlo. Si se activa, el microcontrolador intenta cargar los ajustes en la configuración 0. Si la configuración falla la validación de la suma de comprobación, entonces el MCU volverá a las constantes en tiempo de compilación. Esta función puede desactivarse en el software, si no se desea.

La ventaja de la solución basada en el MCU radica en su extrema flexibilidad. A diferencia de los ASIC del mercado, el MCU puede configurarse con funcionalidades no estándar específicas para la aplicación en uso. Esta aplicación fue desarrollada para la familia de MCUs de propósito general PIC16F15244. El código fuente está disponible en Microchip Discover (discover.microchip.com) y Github.

Convertidor de tensión a frecuencia (V/F)

El convertidor de voltaje a frecuencia (V/F) demuestra el uso de periféricos de hardware para crear una función independiente del núcleo que normalmente tendría que crearse con un circuito integrado externo. Una de las mayores ventajas de esta configuración es que los periféricos se configuran por software, lo que facilita la modificación del ejemplo. Otra ventaja es que el convertidor se implementa en el microcontrolador, lo que reduce la lista de materiales (BOM) y el área de diseño necesaria.

Uno de los retos del enfoque basado en el MCU es que no funciona tan bien como la solución analógica, ya que la resolución de la salida está intrínsecamente limitada por el ADCC. Nominalmente, el ADCC es de 12 bits, pero se ha configurado para una resolución de 14 bits sobremuestreada. Asimismo, el oscilador controlado numéricamente (NCO) que sintetiza la frecuencia de salida tiene una resolución finita y puede tener fluctuaciones en su salida, dependiendo del valor medido por el ADC.

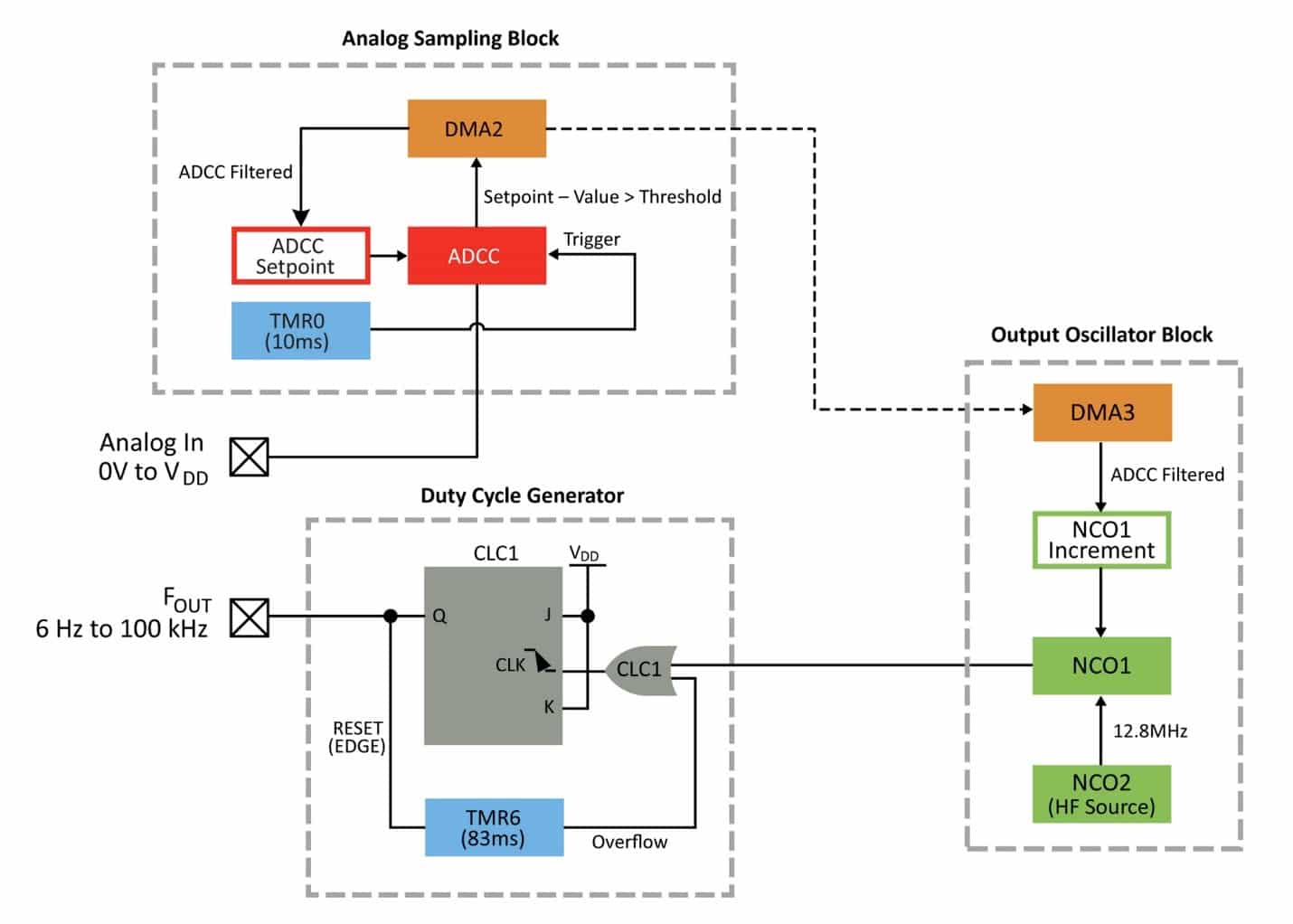

Para implementar esta solución, hay tres bloques distintos de periféricos: un bloque de muestreo analógico, un bloque de oscilador de salida y un generador de ciclo de trabajo.

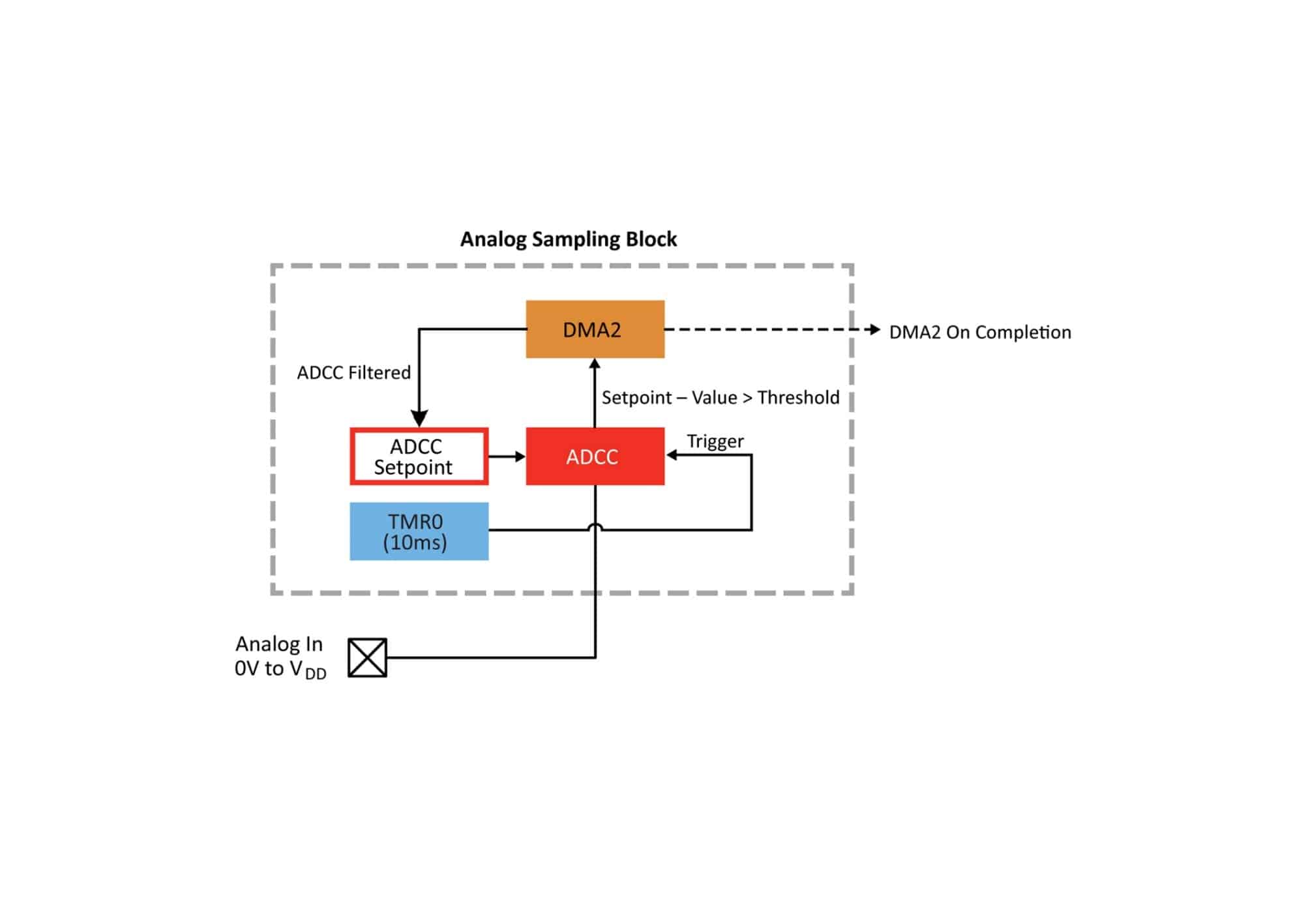

Bloque de muestreo analógico

El bloque de muestreo analógico es responsable de la conversión analógico-digital. Para que una salida de 100 kHz sea posible con los límites de frecuencia del dispositivo, el ADCC se ha configurado para acumular múltiples muestras y luego promediarlas para obtener un resultado sobremuestreado de 14 bits.

Una desventaja de este sobremuestreo es el ruido estadístico adicional que se añade al resultado. El ruido se compensa promediando la sobremuestra y añadiendo histéresis. Para implementar la histéresis, se utiliza la función de interrupción de umbral del ADCC. (Para simplificar, sólo se cubrirán los detalles de cómo este ejemplo utiliza la función de interrupción de umbral).

Cuando el ADCC termina de calcular la sobremuestra promediada, el valor resultante se compara con un registro de consigna en el periférico. Si la diferencia entre los dos es mayor o menor que los umbrales establecidos, entonces se dispara una interrupción. La CPU enmascara esta interrupción y no se ve afectada, sin embargo, esta interrupción desencadena una copia de acceso directo a memoria (DMA) del resultado de la sobremuestra promediada al registro de punto de ajuste del ADCC, que actualiza el punto medio de la histéresis. Si no se superan los umbrales, esta copia DMA no se producirá, lo que no activará la actualización del DMA del bloque oscilador de salida.

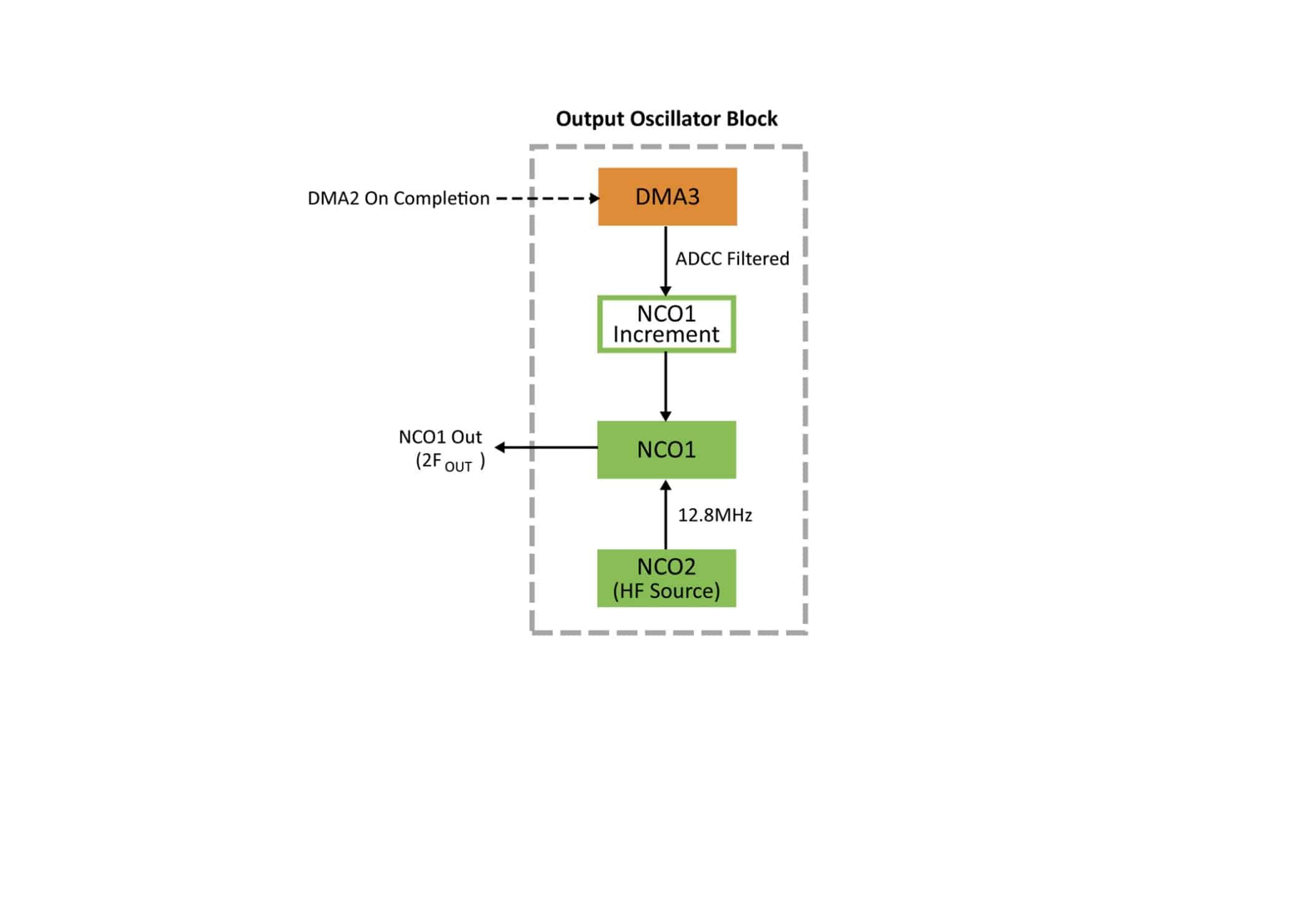

Bloque oscilador de salida

El bloque oscilador de salida de esta solución se encarga de generar una señal de reloj a la frecuencia de salida deseada. Esta señal de salida está conectada internamente al generador de ciclo de trabajo, que reduce a la mitad la frecuencia de salida pero crea una salida con un ciclo de trabajo del 50%. Debido a esto, el bloque oscilador de salida funciona al doble de la frecuencia de la salida.

El corazón del bloque oscilador de salida es un oscilador controlado numéricamente (NCO). El periférico NCO funciona añadiendo un valor de incremento a un acumulador en el flanco ascendente de un reloj de entrada. El desbordamiento del acumulador se utiliza para derivar la salida del periférico. (Para la explicación completa sobre el NCO, consulte la hoja de datos).

En este ejemplo, el NCO2 se ha configurado para crear internamente la frecuencia de reloj de entrada necesaria para obtener una salida de 100 kHz a partir de una entrada de 14 bits. El resultado de 14 bits se utiliza porque el resultado nativo de 12 bits del ADCC no es lo suficientemente grande para generar la salida de 100 kHz sin una fuente de reloj externa.

| Resultado ADC | NCO1 Salida (duplicada) | Frecuencia de Salida |

| 0x0000 | 0 Hz | 0 Hz |

| 0x0001 | 12.2 Hz | 6.1 Hz |

| 0x0100 | 3.1 kHz | 1.6 kHz |

| 0x1000 | 50 kHz | 25 kHz |

| 0x3FFF | 200 kHz | 100 kHz |

Salidas ideales del convertidor V/F de 100kHz,, con el Watchdog apagado.

Si se cambia la frecuencia de salida de NCO2, o se utiliza una fuente alternativa, la frecuencia de salida se escalará a un rango de salida diferente. Por ejemplo, si NCO2 se reduce a 1,28 MHz, la salida alcanza un máximo de 10 kHz.

| Resultado ADC | NCO1 Frecuencia de Salida (duplicada) | Frecuencia de Salida |

| 0x0000 | 0 Hz | 0 Hz |

| 0x0001 | 1.2 Hz | 0.6 Hz |

| 0x0100 | 312.5 Hz | 156.3 Hz |

| 0x1000 | 5 kHz | 2.5 kHz |

| 0x3FFF | 20 kHz | 10 kHz |

Salidas ideales del convertidor V/F de 10kHz,, con el Watchdog apagado.

Generador de ciclo de trabajo

El bloque generador de ciclo de trabajo de esta solución es responsable de la creación de una salida de ciclo de trabajo del 50%. Esta característica es opcional – la salida del NCO puede ser utilizada directamente, aunque el ciclo de trabajo variará en un grado mucho mayor.

Este generador se implementa utilizando una de las Células Lógicas Configurables (CLC). Las CLC son pequeños bloques de lógica discreta configurable, similares a una célula individual de una FPGA (Field Programmable Gate Array). Las CLC pueden utilizarse como puertas lógicas discretas, como AND-OR u OR-XOR. También pueden configurarse como latches o flip-flops. En esta solución, un CLC se implementó como un flip-flop J-K con Reset. J y K se mantienen en lógica ALTA. El bloque oscilador de salida se utiliza como reloj para el flip-flop. Cada pulso de reloj de entrada hace que la salida conmute, lo que genera un ciclo de trabajo del 50%. Nota: el jitter de frecuencia del bloque oscilador de salida afectará al ciclo de trabajo.

El temporizador 6 se utiliza como un temporizador de vigilancia «watchdog». Si la salida no produce un flanco (ascendente o descendente), el temporizador se desbordará y generará un pulso de reloj al CLC. Esto controla el lado bajo del rango de frecuencia de salida. En lugar de llegar a DC, la salida conmuta a la mitad de la frecuencia del temporizador, para una salida de 6 Hz.

Para implementar el ejemplo, se seleccionó la familia de MCUs PIC18-Q43 debido al gran número de periféricos que se utilizan. El código fuente de este proyecto está disponible en Microchip Discover (discover.microchip.com) y Github.

Conclusión

Aunque los microcontroladores y microprocesadores de alto rendimiento están aquí para quedarse, los MCU de 8 y 16 bits son una herramienta inestimable para realizar pequeñas tareas especializadas. Las tareas no son necesariamente complejas, pero pueden requerir mucho tiempo o ser críticas. Al descargar las tareas, los dispositivos de 32 bits pueden tener implementaciones más sencillas que mejoran la fiabilidad, reducen el uso de memoria y disminuyen el consumo de energía.