Autor: Kavita Char, Gerente Principal de Marketing de Producto

Introducción

En los últimos años, la demanda de mayor funcionalidad e inteligencia “on the Edge” o en el borde ha impulsado la necesidad de mayor potencia de procesamiento y memoria en los dispositivos de borde. Las aplicaciones ofrecen mayor cantidad de funciones y los usuarios exigen un mayor nivel de funcionalidad integrada en los productos, incluyendo interfaces gráficas y de usuario sofisticadas, algoritmos de aprendizaje, conectividad de red y un nivel avanzado de seguridad. Más recientemente, el aprendizaje automático está habilitando capacidades de IA de voz y visión en dispositivos de borde que ayudan a estos a tomar decisiones inteligentes en el propio dispositivo y a activar acciones sin intervención humana. Los marcos de software sofisticados son una parte esencial de estas soluciones.

Si bien la potencia de procesamiento es clave para todo este tipo de aplicaciones, también impulsa la necesidad de un almacenamiento rápido, confiable, de bajo consumo y no volátil para código y datos. Al desarrollar sistemas embebidos, la elección de la memoria puede afectar significativamente el rendimiento, el costo, la complejidad del diseño y el consumo de energía. Se necesitan nuevas arquitecturas para abordar las necesidades cambiantes de mayor rendimiento, mayor memoria y menor consumo de energía, manteniendo al mismo tiempo los costos bajos. Se requiere una estrecha colaboración con los fabricantes de memoria para garantizar soluciones totalmente verificadas que cumplan con los requisitos de rendimiento.

Este artículo analizará las diversas arquitecturas de memoria actualmente en uso y las diferentes topologías posibles.

¿Interna o externa?

Memoria flash interna

La mayoría de los MCU tradicionales de propósito general, utilizados en rangos de rendimiento bajos a medios, incorporan memoria flash integrada (normalmente < 2 MB) como el almacenamiento no volátil predilecto para el código. Estos MCU integrados son ideales para la mayoría de las aplicaciones de IoT de rango bajo a medio en diversos segmentos del mercado, como la automatización industrial o de edificios, la medicina, los electrodomésticos o los hogares inteligentes. La memoria flash integrada ofrece varias ventajas (menor latencia, menor consumo de energía, mayor rendimiento) y proporciona una solución más integrada, ideal para aplicaciones más sencillas con limitaciones de espacio y una menor complejidad de diseño. Desde el punto de vista de la seguridad, elimina una superficie de ataque adicional. Por lo tanto, un MCU con memoria flash integrada sigue siendo la solución preferida para la mayoría de las aplicaciones con menores necesidades de rendimiento y funcionalidad.

Sin embargo, la memoria flash integrada tiene un coste, y a partir de cierta densidad de memoria (como 2 MB), su coste empieza a ser prohibitivo. La memoria flash integrada es cara y aumenta la complejidad y los costes del procesamiento de obleas del MCU. Los pasos de fabricación adicionales necesarios para integrar la memoria flash incrementan significativamente el coste del silicio. Además, a medida que surgen nuevas aplicaciones que exigen mayor rendimiento y eficiencia energética, los fabricantes de MCU están adoptando geometrías de proceso más avanzadas y finas, como 28/22 nm o inferiores, para alcanzar un rendimiento mucho mayor e integrar más funcionalidad en el chip. Actualmente, es habitual ver MCU con velocidades de entre 400 MHz y 1 GHz, compatibles con gráficos avanzados, funciones analógicas, de conectividad y de seguridad, así como con protección contra el robo y la manipulación de datos/IP. Si bien esto satisface las necesidades de rendimiento, la integración de memoria en estos dispositivos se convierte en un desafío, ya que la memoria flash integrada no escala bien en geometrías de proceso inferiores. La celda flash no se reduce eficientemente por debajo de los 40 nm, lo que la hace menos viable o más cara en estas geometrías.

Estos desafíos técnicos y de costo para la integración de memoria flash de gran tamaño en chip obligan a los fabricantes a considerar opciones alternativas para sus aplicaciones de alto rendimiento.

Memoria externa

Los diseñadores están considerando nuevas arquitecturas para cerrar esta brecha y cada vez más se inclinan por el uso de memoria flash externa para sus aplicaciones más exigentes y de mayor rendimiento. La compatibilidad con casos de uso más complejos, como gráficos de alta gama, procesamiento de audio o aprendizaje automático, impulsa esta necesidad, y la fuerte disminución en el precio de la memoria independiente impulsa esta tendencia. El uso de memoria externa permite ampliar el espacio de código y datos en un sistema embebido. La memoria flash externa es básicamente una parte del mapa de memoria del MCU que se puede leer directamente y utilizar para el registro de datos o el almacenamiento y la ejecución de software.

Para los fabricantes de productos IoT, la transición a memoria flash externa para sus aplicaciones de alto rendimiento ofrece varias ventajas, como la flexibilidad en la selección de tamaños de memoria y la garantía de futuro de sus diseños. A medida que los desarrolladores añaden más funcionalidades que requieren una mayor huella de memoria, es bastante sencillo cambiar una memoria de menor tamaño por una memoria de mayor tamaño y compatible con pines. También les permite contar con un enfoque de plataforma unificado para sus diversos diseños. Las desventajas son la latencia adicional que implica acceder a la memoria externa (mitigada con memorias cuádruples/octales y un uso cuidadoso de las cachés), un consumo ligeramente superior y el coste adicional de la memoria externa. Esto también aumenta la complejidad del diseño de la placa y requiere un enrutamiento adicional en la PCB, así como prestar atención a la integridad de la señal.

Para los fabricantes de MCU, separar el MCU de la memoria les permite migrar a nodos de proceso más avanzados para obtener mayor rendimiento, mayor funcionalidad, eficiencia energética y menores costes del dispositivo. Como se mencionó anteriormente, la memoria integrada es cara y se vuelve prohibitiva a medida que aumenta el tamaño. La mayoría de los fabricantes de MCU incorporan ahora interfaces SPI cuádruples u octales compatibles con la función de ejecución in situ (XiP), lo que les permite interactuar sin problemas con estos dispositivos flash NOR. Algunos MCU admiten el descifrado sobre la marcha, lo que permite almacenar una imagen cifrada en una memoria flash externa y acceder de forma segura para su ejecución. Esta solución proporciona el alto rendimiento, el bajo consumo y la seguridad avanzada que requieren las aplicaciones edge actuales.

Figura 1: Opciones de memoria – MCU con memoria interna y externa

Además de una importante reducción en el coste de la memoria independiente, se han producido avances en la tecnología de memoria que impulsan esta transición hacia la memoria flash externa. Los dispositivos flash externos admiten la interfaz periférica serial (SPI) para la comunicación con el MCU y están disponibles con interfaces cuádruples u octales, con velocidades de datos simples y dobles que multiplican el ancho de banda por cuatro u ocho. La especificación JEDEC alcanza los 200 MHz, lo que permite un ancho de banda de hasta 400 MHz. Las memorias externas admiten la funcionalidad XiP, que permite ejecutar código directamente desde la memoria flash externa en lugar de copiarlo y ejecutarlo desde la SRAM interna. También admiten lectura y escritura simultáneas (lectura mientras se escribe o RWW), lo que permite la ejecución de código mientras se escribe una parte del mismo. Esto permite actualizar el código en una parte de la memoria sin problemas mientras se ejecuta desde otra. Los dispositivos flash NOR serie están disponibles en una variedad de tamaños de memoria, interfaces y opciones de encapsulado; suelen operar a 1,8 V o 3,3 V y admiten 100 000 ciclos de escritura.

Desafíos de la memoria externa y mitigación

Si bien la memoria externa ofrece numerosas ventajas, existen preocupaciones sobre la latencia asociada a la memoria flash externa y su impacto en el rendimiento general. Es posible mitigar en cierta medida esta limitación del ancho de banda mediante el uso de una interfaz SPI cuádruple u octal, que permite la transferencia de datos a través de 4 u 8 líneas paralelas, en comparación con la línea única de una SPI convencional. Con doble velocidad de datos (DDR), este rendimiento se puede duplicar enviando datos tanto en el flanco ascendente como en el descendente del reloj. Los fabricantes de memorias flash externas también incorporan compatibilidad con modos de lectura en ráfaga para un acceso más rápido a los datos, lo que puede ayudar a reducir la latencia. Se pueden utilizar cachés para mitigar algunos de los efectos de la latencia, pero se requiere una gestión cuidadosa del software para optimizar su uso. Los diseñadores de sistemas también pueden mitigar algunos de los problemas de latencia transfiriendo el código a la SRAM interna y ejecutándolo desde ella para obtener el máximo rendimiento.

También existe la preocupación por el mayor consumo de energía asociado con el uso de memoria flash externa. Los fabricantes de memoria flash prestan especial atención a optimizar el consumo de corriente de los dispositivos, especialmente al operar en modo XiP, incluyendo modos de suspensión de bajo consumo y tiempos de activación rápidos, además de diversas técnicas de diseño de E/S para reducir el consumo de energía.

También existen algunos riesgos de seguridad asociados con la memoria externa. El uso de memoria externa añade una superficie de ataque adicional que crea una vulnerabilidad que puede ser explotada por hackers y que debe protegerse. Esto requiere que los fabricantes de MCU añadan capacidad de cifrado/descifrado a la interfaz SPI cuádruple/octal, para que el código cifrado pueda almacenarse y transferirse de forma segura.

Uso de memoria flash externa con microcontroladores RA

Los microcontroladores de la familia RA de Renesas integran memoria flash integrada, así como múltiples interfaces de memoria a memoria externa, para ofrecer la máxima flexibilidad y rendimiento. Admiten interfaces SPI cuádruples u octales para un mayor rendimiento de datos, utilizando cuatro u ocho líneas de datos en lugar de la única línea habitual con la interfaz SPI. Esto mejora significativamente el rendimiento, especialmente en aplicaciones que requieren accesos rápidos a la memoria, como gráficos, audio o registro de datos.

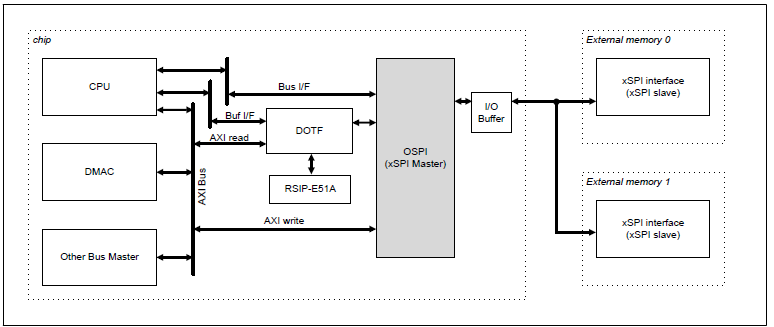

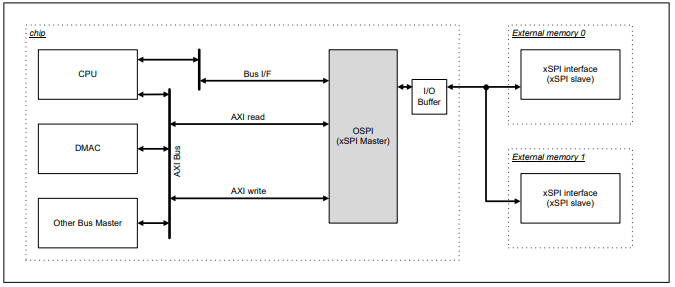

Todos los microcontroladores de la serie RA8 incluyen una interfaz SPI octal compatible con xSPI. El protocolo xSPI (Interfaz Periférica Serie Expandida) especifica la interfaz con dispositivos de memoria no volátil y permite un alto rendimiento de datos, un bajo número de señales y una compatibilidad limitada con dispositivos SPI heredados. Esta interfaz eléctrica, compatible con los estándares JEDEC JESD251 (Perfiles 1.0 y 2.0), JESD251-1 y JESD252, puede ofrecer un rendimiento de datos brutos de hasta 200 Mbytes por segundo. En algunos MCU RA8, la interfaz Octal SPI también admite la función de descifrado sobre la marcha (DOTF), que permite importar de forma segura imágenes cifradas almacenadas en una memoria flash externa para su ejecución. Las figuras a continuación muestran la interfaz Octal SPI en los MCU RA8, con y sin DOTF. Se pueden conectar dos dispositivos de memoria externa a la interfaz Octal SPI mediante la selección de chip, como se muestra a continuación, lo que ofrece mayor flexibilidad a los diseñadores.

Figura 2: SPI Octal con DOTF Figura 3: SPI Octal sin DOTF

Figura 3. SPI Octal sin DOTF

La interfaz SPI Octal de los MCU RA8 admite la operación de ejecución in situ (XIP) y puede comunicarse con hasta dos esclavos mediante señales de selección de chip. Los modos compatibles son:

- 1/4/8 pines con SDR/DDR (1S-1S-1S, 4S-4D-4D, 8D-8D-8D)

- 2/4 pines con SDR (1S-2S-2S, 2S-2S-2S, 1S-4S-4S, 4S-4S-4S)

Los tipos de memoria compatibles son Octal Flash y Octal RAM, así como HyperFlash e HyperRAM. La interfaz SPI Octal puede direccionar hasta 256 MB de espacio de direcciones para cada CS y admite la función de precarga para lectura en ráfagas con baja latencia y un excelente búfer para escritura en ráfagas con alto rendimiento. Además de las interfaces de memoria flash interna y externa, los MCU RA8 también incluyen memoria TCM (memoria estrechamente acoplada) y cachés I/D que optimizan el rendimiento. La TCM es una memoria de estado de espera cero y tiene la latencia más baja de todas las memorias en chip. Por lo tanto, puede utilizarse para las partes más críticas del código.

Topologías de memoria

Se pueden configurar múltiples y flexibles configuraciones de memoria utilizando diversas memorias e interfaces de memoria disponibles en los MCU de la serie RA8, como se muestra en la Figura 4.

Figura 4: Topologías de memoria posibles con MCU RA8

En la configuración más típica, el código se almacena y se ejecuta desde la memoria flash interna integrada, lo que permite un sistema simple, de baja latencia, altamente seguro y de bajo consumo. Sin embargo, esta no es una solución escalable, y cualquier aumento del tamaño del código que supere el tamaño de la memoria flash integrada deberá abordarse con memoria externa.

En la segunda configuración, el código se almacena y se ejecuta desde la memoria flash externa. Esta es la capacidad XiP y es la opción más flexible y escalable. La memoria externa puede simplemente sustituirse por un dispositivo compatible con pines y de mayor densidad a medida que aumenta el tamaño del código, lo que permite una solución rentable que se puede actualizar fácilmente sin necesidad de rediseñar las placas. Esto conlleva un consumo de energía ligeramente superior y una mayor latencia que podría afectar al rendimiento general.

En la tercera configuración, el código se almacena en la memoria flash externa y se transfiere a la SRAM interna o TCM para su ejecución. Esto proporciona el máximo rendimiento porque el código se ejecuta desde la SRAM rápida. Sin embargo, existe una limitación en el tamaño del código, basada en el tamaño de la SRAM, y una mayor complejidad del software si el tamaño del código excede la SRAM o el TCM disponibles. Los tiempos de reactivación también podrían aumentar, ya que el código perdido al apagar la SRAM tendría que recargarse en cada ciclo de encendido.

Conclusión

No existe una única respuesta correcta a la hora de seleccionar las opciones de memoria. Si bien la mayoría de las aplicaciones de IoT de gama baja a media pueden usar memoria flash interna, muchas aplicaciones de mayor rendimiento requieren el uso de memoria flash externa. La selección de la memoria se basa en varias consideraciones: los requisitos de la aplicación, el tamaño de memoria necesario, el rendimiento esperado, la arquitectura del sistema, los objetivos de consumo de energía, las preocupaciones de seguridad y los planes futuros de productos/plataformas, son solo algunas de ellas. Ambas opciones tienen ventajas y desventajas: la memoria flash interna proporciona simplicidad y una solución altamente segura, perfectamente integrada y adecuada para una amplia gama de aplicaciones, mientras que la memoria flash externa ofrece flexibilidad, expansión de memoria y escalabilidad para aplicaciones emergentes de IoT e IA de borde. Al comprender estas ventajas y desventajas, los desarrolladores pueden tomar decisiones informadas y alineadas con los objetivos de sus proyectos.