Discontinuities in the design flow become increasingly disruptive and expensive during the development of complex signal processing and communications technologies. As design cycles are shorter, the impact of these discontinuities is magnified. This article describes some specific applications (algorithm design, systems architecture, and hardware design) that illustrate the recent and significant advances in terms of tools and methods for modeling, simulation, and code generation. For algorithm design, several hundred ready-to-use system objects for signal processing and communications are already available in MATLAB to enable faster development of complex algorithms. System architects can now model baseband and RF system components in a unified environment, as well as perform true multi-frequency simulations. In terms of hardware design, recent advancements such as the workflow wizard, critical path highlighting, distributed pipeline, remediation logging, and resource utilization reports provide an integrated framework for achieve faster design and prototyping iterations.

Design of algorithms for streaming systems

Many engineers begin the development of signal processing and communications algorithms in MATLAB using floating-point arithmetic. These algorithm developers can take advantage of MATLAB's robust signal acquisition and analysis capabilities, as well as the built-in algorithm libraries of various toolboxes. However, in some organizations, these algorithms are later rewritten in C code to adjust them for implementation, conversion to integer or fixed-point arithmetic, or integration with other design elements. This rewrite step is the perfect example of a potentially costly and disruptive discontinuity in the design flow.

System Objects, a major recent addition to MATLAB, allow engineers to model signal processing systems for streaming applications directly in MATLAB, as well as use several hundred new library components for signal processing, processing image and video, and communications.

By way of example, Figure 1 shows a block diagram representing a basic communications system with a transmitter, a channel and a receiver as components. In order to model and simulate a system like this, some engineers write many thousands of lines of C code, and then look for ways to integrate the design with test equipment or to analyze the simulation results.

In contrast, relative to the several thousand lines of C code typically written, the MATLAB code shown in Figure 2 uses a variety of system objects available in the DSP System Toolbox and Communications System Toolbox. For example, to model the transmitter, an engineer can instantiate the Communications Blockset Reed-Solomon Encoder, Convolutional Encoder, Block Interleaver, Rectangular QAM Modulator, and Orthogonal Space-Time Encoder system objects and call them one after the other. , as shown in Figure 2.

Also, unlike traditional styles of functional programming, MATLAB's system objects are object-oriented implementations of algorithms; they implicitly handle indexing, buffering, and state management, which makes code much easier to write, debug, and maintain. The structure of the code allows engineers to easily compare it to the original specification or block diagram. Algorithm designers can quickly combine this code with their existing MATLAB code and test the algorithms with dynamic data acquired using measurement instruments.

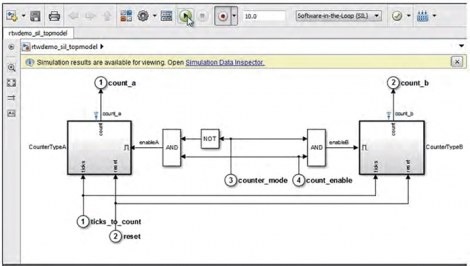

Algorithms coded using system objects facilitate code reuse throughout the system design process. Fixed-point or floating-point MATLAB code can be included directly into a Simulink model as part of the system architecture, modeling, and design process.

Engineers can also automatically generate C code from MATLAB code that uses system objects using MATLAB Coder, and then use that C code for simulation or integration with other C/C++ design elements after proper verification.

RF and digital systems architecture

Budgeting for static links is a common first step in RF designs based on specifications for LTE, Bluetooth, ZigBee, Wi-Fi, or other technologies. This calculation is a good starting point, but it does not include modulation of input signals, imaging effects, and other real-world phenomena. In order to effectively model and simulate the impact of RF issues on communications systems, system architects today juggle various disconnected tools that support digital or analog RF designs, but not both.

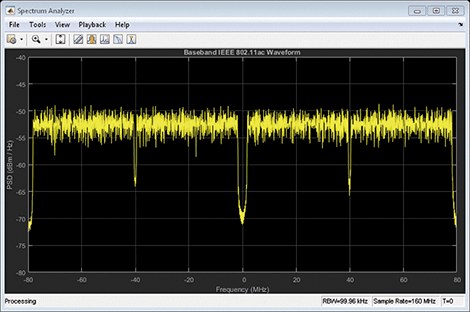

SimRF is a versatile environment that provides equivalent baseband modeling capabilities and circuit covers, enabling simulation of multi-frequency dynamics in RF receivers and XNUMX-port components such as mixers. SimRF and Simulink together provide a common environment for modeling and simulating RF and baseband systems in a unified design. Using these tools together enables system architects to perform realistic simulations early in the development process, as well as make informed tradeoff decisions on designs that include digital and analog RF components.

Figure 3 shows the complete system model of an ISM band low IF receiver including both the digital signal processing components and the RF receiver subsystem. Details of the RF subsystem that implements a Hartley IF receiver are also shown. Unlike traditional IF receiver modeling methods that employ cascades of two-port elements and single-frequency approximations, the use of three-port elements simplifies the model of the receiver. This model also employs circuit jacket simulation technology and supports multi-frequency modeling.

System architects can also explore the feasibility and relative advantages of alternative approaches to image rejection, such as a heterodyne or direct conversion architecture in the unified environment. In addition to simulating the effects of RF problems, system architects can use the same system models used for design to perform simulation verification tasks that would normally be performed in a laboratory environment.

hardware design

After algorithm design and system architecture are complete, the next step in many development cycles is FPGA implementation and verification of the digital parts. Among the leading causes of inefficiency in FPGA prototyping and deployment are the slow design iterations required to find the right balance between power consumption, performance, and footprint.

Figure 5 shows a symmetric FIR filter implemented in fixed-point arithmetic. To implement such a filter in hardware, engineers must carefully balance performance and latency, as well as monitor the amount of hardware resources used. Critical path highlighting is one of the key features that provides actionable insights into potential bottlenecks in the system. Using the post-synthesis information generated by the Xilinx ISE synthesis tool, Simulink HDL Coder annotates the timing of critical paths in the Simulink model. Engineers can use this information in conjunction with pipeline techniques to partition critical path layouts and latencies. Figure 6 shows the same filter layout, with critical paths automatically highlighted, along with the estimated latency for each path segment.

As mentioned above, pipeline is one of the key techniques engineers use to deal with critical path latencies. One of the known challenges with pipelines is that parallel paths can have disparate latencies, which could lead to unexpected or unwanted system behavior. Distributed pipeline, which is a frequently used technique to solve this problem, can now be automated. By choosing this option, engineers can automatically reschedule the model and balance latencies introduced by pipeline records from the relevant parallel paths.

In the past, these types of design iterations and tradeoff evaluations required a significant amount of time and effort. Figure 7 shows a new workflow assistant console that allows engineers to perform design iterations much faster and more intuitively.

This is especially useful for those who are not HDL programming experts but need to take advantage of FPGA processing. In addition to using critical path highlighting and distributed pipeline, engineers can also examine an automatically generated resource utilization report (such as the one shown in Figure 8) to monitor the type and number of critical hardware components used , as well as determine the best architecture option for a given situation by rapidly iterating through several viable design options.

Design acceleration in teams

Today's engineering managers are challenged with coordinating geographically dispersed teams working on different parts of a global system using various disconnected tools.

In many cases, system-level designs are best done in graphical environments, while some lower-level details are best expressed as text in MATLAB or C. This article presents some new advances that improve inefficiencies in various stages of the design flow.

In the case of algorithm design, system objects are a key new development for the modeling and simulation of communication and signal processing systems. Several hundred ready-to-use system objects for signal processing and communications are already available in MATLAB. In addition, system objects support fixed-point arithmetic, which provides equivalent baseband and circuit coverage, is an important new tool for achieving more efficient system architecture workflows. It enables engineers to model baseband and RF system components in a unified environment, as well as perform true multi-frequency simulations.

In order to improve design iteration cycle times in hardware design and FPGA/ASIC prototyping, there are several recent advancements including workflow wizard, critical path highlighting, distributed pipeline , remediation logging, and resource utilization reports, which provide a framework and critical actionable information about system performance and resources used.

Whether teams are large or small, geographically distributed or co-located, engineering organizations faced with discontinuities in their design workflow can apply these technologies to simplify and accelerate the development of complex systems. communications and signal processing.