Recently, Renesas has expanded its popular RZ microprocessor (MPU) family with a new device aimed at high-performance robotic applications. Delivering superior performance within the family, the new RZ/V2H microprocessor enables real-time control and vision AI. The new RZ/V2H MPU will also be a highlight at the Renesas booth at this year's Embedded World in Hall 1, Booth 234 (1-234). We had the opportunity to speak with Keigo Kawasaki, Chief Marketing Officer at Renesas, about the new addition to the RZ family and its new unique features for the area of robotics applications for further evolution of AI.

Q: More and more semiconductor companies are offering AI processors. What differentiates Renesas from the competition?

There are three USPs to highlight:

- “DRP-AI 3” AI Accelerator with “Pruning” Technology: Pruning is a hardware-based approach to enable lightweight AI models and improve AI computing efficiency. This also affects an energy efficiency of 10 TOPS/W, achieving a 10 times greater improvement than previous models.

- Image processing acceleration in addition to AI acceleration: To increase the performance of the entire imaging system, the RZ/V2H includes the OpenCV accelerator, along with the free OpenCV acceleration library.

- Plus Arm Cortex-A55 with quad 1,8 GHz cores for applications where robust real-time control performance is required with three dual-core 8 MHz Cortex-R800 processors and one Cortex-M33 processor to handle less demanding tasks. intensive, such as reading sensor data. Renesas' new RZ/V2H is the only heterogeneous AI processor to be equipped with all three Cortex products (A, R, M) from Arm.

Q: What are the challenges in implementing AI vision, especially in embedded systems? What is the Renesas solution?

Heat generation is a major challenge in embedded systems. Since high-performance processors generate heat, engineers often face challenges in offsetting the heat, either by reducing performance or adding components that dissipate heat, which in turn increases the cost and size of the system. With Renesas RZ/V2H, they can easily achieve 10 TOPS/W performance without cooling fans.

Q: What applications require real-time image processing?

On the one hand, industrial robots for factory automation and service robots for restaurants and commercial facilities. These are robots that can recognize surrounding objects and obstacles in real time and move autonomously. On the other hand, drones and small transport vehicles also need to think independently and operate in real time. The RZ/V2H is ideal for these applications.

Q: What kind of feedback did you receive from customers?

Many customers have already decided to adopt our AI modules for industrial applications and small HSR (Human Support Robot) modules. There are also more than 40 customers who are considering our products. The deciding factor in all these negotiations is the fact that the RZ/V2H can significantly reduce heat generation.

Q: What is accelerating the widespread adoption of vision AI applications? What is Renesas' strategy?

A major challenge is that engineers often struggle to use AI effectively due to the need for specialized AI skills. Renesas offers a number of AI application libraries for free to address customer challenges.

Q: Tell us about your future roadmap.

On the technology front, we will continue to pursue TOPS/W to improve energy performance. In the future, we expect embedded devices to have applications that require more computing performance, such as generative AI. In terms of searching for new products, we will continue to address the demands of our customers and the market.

Q: What are the benefits of Renesas' patented DRP technology?

DRP (dynamically reconfigurable processor) can run applications while dynamically changing the circuit connection configuration of the on-chip arithmetic units at each operating clock according to the content to be processed. Because only the necessary arithmetic circuits are used, DRP consumes less power than CPU processing and can achieve higher speeds. Furthermore, compared to CPUs, where frequent accesses to external memory due to cache misses and other causes will degrade performance, DRP can create the necessary data paths in the hardware in advance, resulting in less degradation. performance and less variation in operating speed (jitter). due to memory accesses.

The DRP also has a dynamic reconfigurable feature that changes the circuit connection information each time the algorithm changes, enabling processing with limited hardware resources, even in robotic applications that require processing of multiple algorithms.

DRP is particularly effective in streaming data processing, such as image recognition, where parallelization and pipelined directly improve performance.

Q: What are the benefits of a heterogeneous architecture where DRP-AI 3, DRP and the CPU work cooperatively?

A: Service robots, for example, require advanced AI processing to recognize the surrounding environment. On the other hand, algorithm-based processing that does not use AI is also required to decide and control the robot's behavior. However, current embedded processors (CPUs) lack sufficient resources to perform these various types of processing in real time. Renesas solved this problem by developing a heterogeneous architecture technology that allows the dynamically reconfigurable processor (DRP), AI accelerator (DRP-AI), and the CPU to work together.

DRP AI accelerates AI vision processing. Renesas has applied its proprietary DRP technology to develop the OpenCV accelerator that accelerates processing of OpenCV, an open source industry standard library for computer vision processing. The resulting speed improvement is up to 16 times faster compared to CPU processing. The combination of DRP-AI and OpenCV Accelerator improves both AI computing and image processing algorithms, enabling real-time, energy-efficient execution of Virtual SLAM used in applications such as robot vacuum cleaners.

On the other hand, programs such as robot behavior decision and control require processing as conditions change and process details in response to changes in the surrounding environment. CPU software processing may be better suited for this than hardware processing as in DRP. It is important to distribute processing in the right places and operate in a coordinated manner. Renesas' heterogeneous architecture technology allows DRP and CPU to work together.

Q: Does Renesas have plans to develop a Neural Processing Unit (NPU)?

“NPU” is a generic term for specialized hardware IP for AI processing, and DRP-AI is a type of NPU.

Q: What are the new DRP-AI 3 applied technologies incorporated in RZ/V2H?

A: DRP-AI3 introduces new high-speed, low-power methods that support major core AI model methods. Specifically, the following basic methods are supported:

1) Quantization: Lower bit weights for the neural network weight information (weight) and input/output data (feature map) for each layer. Switching from 16-bit floating point arithmetic in conventional DRP-AI to 8-bit integer arithmetic (INT8).

2) Branch cutting: a technique to skip calculations by setting the weight information (branches) to zero that does not affect the recognition accuracy.

More detailed technical content was presented at ISSCC 2024 (International Solid State Circuits Conference 2024), the leading international conference on semiconductor circuits, held from February 18 to 22, 2024. The press release was published on February 22, 2024 .

Q: Are there any winning combinations for RZ/V2H already available?

A: Renesas has developed the “Visual Sensing Single Board Computer” that uses camera images to identify your environment and determine and monitor your movements in real time. This solution combines the RZ/V2H with power management ICs and VersaClock programmable clock generators to support energy-efficient industrial robots and machinery. Its efficient design eliminates the need for an additional cooling fan, keeping the bill of materials and solution size small.

This winning combination will be displayed at the Renesas booth at Embedded World 2024 in Hall 1, Booth 234 (1-234).

Q: What about the RZ/V series range?

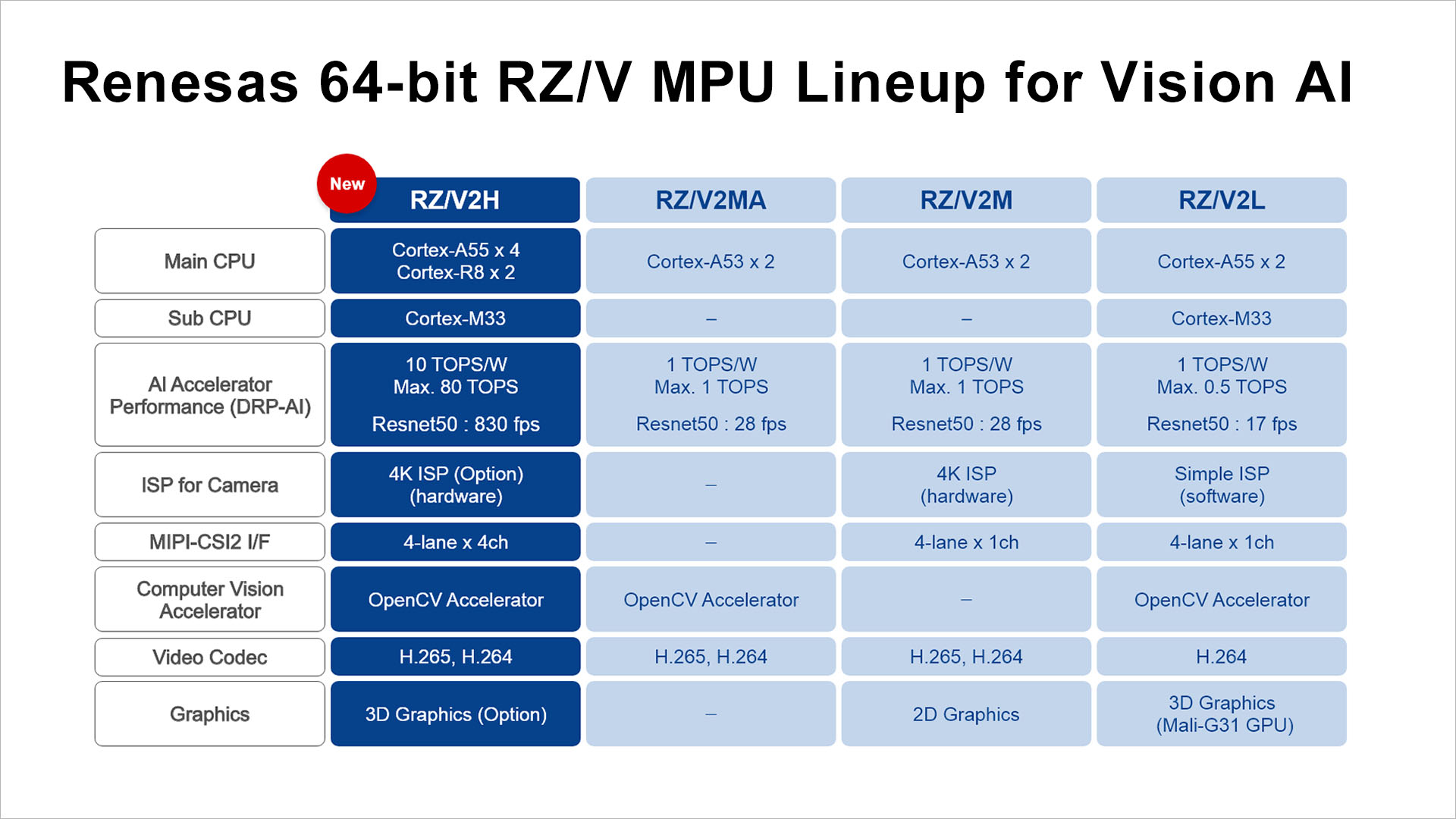

A: The RZ/V series are MPUs that incorporate a DRP-AI accelerator. There is a scalable line from 0,5 TOPS to 80 TOPS with the same architecture.