Comparadas con las técnicas tradicionales de conexión, las interconexiones flip-chip ofrecen una alternativa mejor cuando se requieren unas prestaciones eléctricas superiores y una elevada densidad de señal. Sin embargo, si la planificación de E/S del chip no está bien planteada y optimizada para la aplicación, puede verse muy afectada la ventaja que representa la eliminación de las conexiones inductivas que convierten a flip-chip en una elección ideal para la interconexión.

Las aplicaciones que precisen una impedancia de la línea de transmisión inferior a 50Ω y una baja diafonía entre señales necesitan un enrutamiento de estas señales en modo stripline. El enrutamiento en stripline exige colocar los terminales (bumps) sobre el chip, de manera que exista un escape óptimo desde el chip en modo stripline. Por tanto, la disposición de los terminales de E/S en el chip debe ser prioritaria en función de las prestaciones necesarias: las señales menos críticas pueden salir como microstrip y las más críticas como stripline.

Una disposición inadecuada provocará el escape no deseado de las señales críticas, lo cual en última instancia afectará a las prestaciones de la señal y/o exigirá que el encapsulado utilice más capas en el sustrato de lo necesario. Esto puede provocar un importante aumento en el coste del producto.

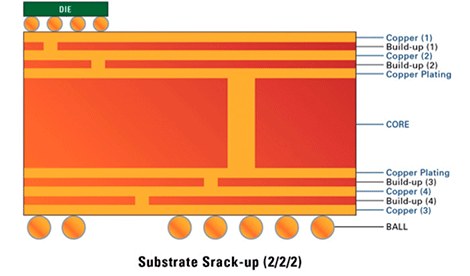

Los dispositivos con interconexiones flip-chip suelen unirse a un sustrato de encapsulado fabricado mediante tecnología de sustrato de construcción secuencial (Sequential Build-Up, SBU). Un único núcleo se convierte en circuitos mediante procesos convencionales de fabricación de sustratos, y se utiliza a su vez como base para construir capas de circuito más densas. Las capas de dieléctrico se depositan simétricamente sobre las caras superior e inferior del núcleo, conservando la planitud mecánica mediante un equilibrio de esfuerzos, bien sea como líquido o como película seca, y luego se cura. A continuación se forman las vías mediante taladrado láser a través de las capas de dieléctrico depositadas para conectar la circuitería entre capas. La circuitería se deposita sobre cada capa utilizando un proceso semiaditivo. Este proceso de añadido secuencial de dieléctrico y capas metálicas facilita el enrutamiento de las pistas metálicas con geometrías mucho más finas, con una anchura de pista de hasta 12um, que no es factible con procesos convencionales de grabado.

Optimización del enrutamiento de señal para aplicaciones de alta frecuencia

Cuando se optimiza para la integridad de señal en aplicaciones de alta frecuencia, los principales objetivos son el control de la impedancia de interconexión y la minimización de la diafonía. Si el sistema está diseñado para trabajar en un entorno de 50Ω, cada pieza del canal del transceptor debe adaptarse a esta impedancia. Cualquier cambio de impedancia en la ruta de señal provocará un excesivo nivel de reflexiones que pueden destruir los datos, y dependiendo de la gravedad del cambio de impedancia, incluso el fallo total del sistema.

Suponiendo un entorno sin pérdidas, la impedancia de interconexión es sencillamente una relación entre la inductancia de la estructura y su capacidad. La inductancia se controla mediante la zona del bucle formada por la señal y su ruta de retorno. La capacidad depende sobre todo de la anchura de la pista, la distancia a la ruta de retorno y la constante dieléctrica del material que rellena el hueco entre la pista y su ruta de retorno. Cuanto mayor es la anchura de la pista, más alta es su capacidad y más baja es su impedancia, y viceversa.

Por tanto, ¿qué hace falta para obtener una pista de 50Ω en un sustrato flip-chip de tipo SBU enrutado en formato microstrip (las capas más externas)? La respuesta es: una anchura de pista con una anchura de hasta 60um.

En enrutamiento de pistas con esta anchura de pista no solo incrementa la superficie ocupada por el sustrato a patillas de escape efectivas sobre un dispositivo con un gran número de E/S, sino que también implica una mayor proximidad de enrutamiento entre las pistas de señal, lo cual incrementa a su vez de manera sustancial el ruido de diafonía.

Además si la aplicación requiere una impedancia de 30Ω es prácticamente imposible enrutar una impedancia tan baja utilizando anchuras realistas de las pistas. En un entorno microstrip, la capacidad de la pista solo está en un acara de la pista y depende por complete de la anchura de esa pista.

La integración de la pista en el sustrato y su enrutamiento en formato stripline resolverán este problema. Ello se debe a que un entorno stripline aprovecha la presencia de planos de la ruta de retorno a ambos lados de la pista, con lo cual en la práctica se duplica la carga capacitiva y se logra una impedancia mucho más baja para las mismas anchuras de pista.

Decisiones para la planificación del CI

La presencia de una ruta limpia de retorno es fundamental para controlar la impedancia de la pista y para evitar problemas relacionados con la integridad de señal. Una sección transversal de SBU en 1-2-1 tiene la capa superior seguida de un núcleo con 2 lados y a continuación la última capa, a la que están unidas las bolas de soldadura. Generalmente las capas del núcleo no se utilizan para enrutamiento de señal y se suelen reservar para las conexiones del dispositivo a alimentación y masa.

Por tanto, en teoría solo hay una capa de enrutamiento, que es la 1ª capa de microstrip, y si el sistema necesita una impedancia de canal de 30Ω sería prácticamente imposible lograrla en un sustrato de tipo 1-2-1.

Al añadir a la construcción otra capa de enrutamiento, como en un sustrato 2-2-2, las pistas se podrían integrar en un formato stripline sobre la capa 2, lo cual permite obtener rutas de baja impedancia.

Para dispositivos con un área de terminales limitada, el paso y el número de E/S definen el tamaño del chip. A medida que aumenta el tamaño del chip se incrementa su coste de forma proporcional. En un intento por optimizar el coste, las patillas de E/S se sitúan en anillos concéntricos, de manera que se reduce el tamaño del chip y al mismo tiempo se logra la misma funcionalidad.

Para un paso determinado en el área de terminales, las restricciones actuales para la fabricación masiva pueden permitir el enrutamiento de hasta dos anillos sobre una sola capa del sustrato SBU. Se pueden colocar cuatro anillos con dos capas de enrutamiento del sustrato SBU, y así sucesivamente.

Un dispositivo con cuatro anillos concéntricos de E/S necesitarían un apilamiento SBU de 3-2-3 como mínimo. Los dos anillos exteriores escaparán sobre la capa 1 del apilamiento del sustrato en formato microstrip. Con el fin de proporcionar una clara referencia al enrutamiento en la capa 1, la capa 2 se suele reservar como ruta de retorno. La capa 3 podría ser otra capa de enrutamiento y la 4ª capa pertenece al núcleo del sustrato. El apilamiento en 3-2-3 proporciona efectivamente dos capas de enrutamiento para las patillas de E/S sobre el chip como escape y conexión a las bolas del encapsulado.

Las pistas que necesiten una baja impedancia serán más adecuadas apropiadas para enrutamiento en las capas interiores. Pero si los terminales de E/S se hallaran en la periferia exterior del chip, sería casi imposible enrutarlas en formato microstrip y aun así lograr la baja impedancia deseada. Por tanto en la práctica es necesario integrarlas en modo stripline.

Al utilizar la misma disposición de E/S, pero con el deseo de tener las filas exteriores de E/S en formato stripline, el sustrato SBU tendrá que ser un apilamiento en 4-2-4. La capa 1 es para la ruta de retorno, la capa 2 es para el enrutamiento de la pista de baja impedancia, la capa 3 se reserva para otra ruta de retorno; la capa 4 se usa para el enrutamiento de otra señal y a continuación está la capa del núcleo. Por tanto, para la misma disposición de E/S aumenta el número de capas en el sustrato SBU, lo cual a su vez incrementa enormemente el coste del encapsulado.

No obstante, si la planificación del chip se hubiera diseñado de tal manera que las E/S que necesiten rutas de baja impedancia se hubieran reservado para los dos anillos concéntricos interiores, y no para los dos exteriores, desaparecería la necesidad de añadir sustrato extra, con lo que se reduce el coste del encapsulado y se logran las prestaciones de señal deseadas.

En resumen, es primordial que la planificación del chip tenga en cuenta las prestaciones del sistema, así como seguir un proceso de diseño interactivo entre los equipos de diseño del CI y de encapsulado del dispositivo con el fin de optimizar las prestaciones del producto y minimizar el coste.

También es preciso tomar decisiones parecidas que tengan en cuenta la planificación en la unión entre el encapsulado y la placa para una perfecta integración de cada componente en el sistema.