La demanda de memoria digital basada en NAND está en auge, impulsada por el aumento del uso de dispositivos que abarcan los mercados de consumidor y móviles, sector industrial y de automoción, y el emergente de Internet de las Cosas (IoT).

Desde que Toshiba introdujo NAND en 1984, el panorama de la tecnología y el mercado ha evolucionado significativamente. Las densidades de bits NAND han aumentado más de 2000 veces debido al tamaño del nodo de proceso pasando de 700nm a 15 nm, y la introducción de nuevas tecnologías a nivel de celda.

Acompañando a este aumento de la densidad ha estado una dramática reducción en el precio por Gb, que ha disminuido aún más rápido que lo que se ha incrementado la densidad de bits – haciendo de NAND el medio de almacenamiento de elección para muchas aplicaciones.

Sin embargo, aunque el precio por bit ha disminuido, pasar a las últimas tecnologías y nodos de proceso, no es tan sencillo. Uno de los principales retos para aquellos que quieran utilizar los últimos diseños NAND puros en sus dispositivos es que las nuevas tecnologías NAND tienden a necesitar motores más potentes de código de corrección de errores (ECC) en los controladores – y esto se ha convertido en una “carrera sin fin”, en general, ya que a menudo hay un período de espera para que los controladores se pongan al día.

Por ejemplo se requiere sólo 1 bit ECC por 512bytes para celdas de un solo nivel (SLC) NAND hasta 43nm,. Esto aumenta a 8bits ECC por 512bytes para NAND SLC de 24nm, haciendo el cambio de 43nm SLC NAND pura a 24nm SLC NAND pura, causando un impacto negativo significativo en el rendimiento, a menos que se implemente una tecnología de controlador más avanzada.

Nivelación del desgaste

Aunque existe la tecnología para hacer NAND en los nodos de proceso aún más pequeños, la disminución de la resistencia y fiabilidad de las celdas entra en juego. Y más aún, las celdas NAND que pueden almacenar varios bits se han desarrollado – la celda NAND de un solo nivel (SLC) puede almacenar 1 bit por celda, la celda NAND multinivel (MLC) puede almacenar 2 bits por celda, mientras que las celdas NAND de triple nivel (TLC) pueden almacenar 3 bits por celda. Sin embargo, la resistencia de escritura / borrado se ve afectada por este tipo de enfoques – SLC puede soportar alrededor de 60.000 ciclos, MLC 3000 ciclos y TLC 500 ciclos (suponiendo el mismo algoritmo ECC).

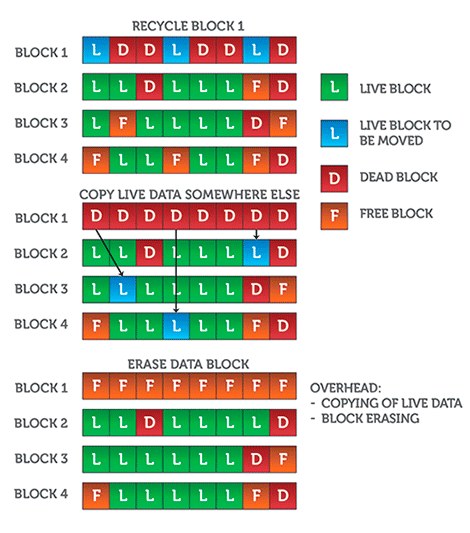

Debido a que los bloques de memoria NAND se pueden degradar y dañar, se asigna un límite superior en el número de escrituras de cada posición de memoria NAND. Los algoritmos de “nivelación del desgaste” también necesitan ser construidos en los controladores NAND para asegurar que las posiciones de memoria NAND se utilizan de manera uniforme.

En el cálculo de la vida útil del sistema utilizando fiabilidad NAND, es importante recordar que las funciones de gestión de memoria causan más escrituras en cada celda que el número de bits de datos que se escriben en un principio.

Esto se debe a que las funciones de gestión de memoria pueden implicar mover datos de un lugar a otro, dando lugar a múltiples escrituras de celdas por cada bit de datos a almacenar.

Mientras escritura / programación de NAND se lleva a cabo sobre una base de página por página, las funciones de borrado eliminan bloques enteros (que constan de varias páginas).

Cuando se prepara un bloque para su borrado, los datos que deben conservarse, se copian primero en otros bloques. Este arrastre de página antes del borrado del bloque se llama recolección de basura (garbage collection).

La reducción de la carga en el controlador

Para muchas aplicaciones existentes que utilizan memoria SLC NAND, tales como diseños industriales, procesadores de comunicaciones y sistemas de automoción, el ECC de 1 bit se implementa en el software del huésped sin ningún efecto significativo en el rendimiento de la aplicación.

La migración a memorias “punteras” que requieren de 4, 8 o incluso 24 bits ECC aumenta significativamente la demanda en el procesador, reduciendo el rendimiento. Con el fin de evitar esta penalización de rendimiento, los chips NAND con ECC integrado se han convertido en la solución preferida.

BENANDTM de Toshiba (con NAND ECC integrado) ofrece una solución de este tipo y elimina la carga del ECC del procesador principal sin necesidad de un controlador de hardware adicional.

BENAND utiliza la bien establecida, interfaz NAND común, asegurando la compatibilidad con SLC NAND Flash pura en áreas como conjuntos de comandos, funcionamiento del dispositivo, encapsulado y configuración de pines. El sistema central se encarga de cuestiones como la gestión de bloques defectuosos, la nivelación del desgaste, asignación de dirección y la recolección de basura en la misma forma que con SLC NAND pura.

Los dispositivos BENAND están disponibles desde 1 Gb a 8 Gb de densidad, encapsulados como dispositivos estándar TSOP-I-48-P y BGA de 63 bolas que son compatibles en pines con los conocidos encapsulados SLC.

También está disponible una pequeña versión BGA de 67 bolas 6,5mm x 8,0mm, lo que permite a los diseñadores cumplir con las reducidas limitaciones de espacio en los nuevos diseños. La compatibilidad directa de pin y encapsulado entre SLC NAND pura y BENAND permite su reemplazo directo cuando se actualiza a FLASH de última generación.

Este enfoque ha permitido a los ingenieros de Toshiba ayudar a los clientes a integrar BENAND tanto en los diseño existentes como en los nuevos, ofreciendo los beneficios de migrar a la última tecnología, a la vez que evita los altos costes asociados con un rediseño significativo del sistema o el uso a largo plazo de la tecnología legada.

Eliminando la necesidad de un controlador NAND

Los controladores embebidos realizan operaciones tales como la corrección de errores, la nivelación de desgaste y la gestión de bloques defectuosos para garantizar que la memoria NAND funciona correctamente.

Las soluciones e.MMC se basan normalmente en MLC NAND y combinan MLC NAND pura con un controlador NAND. Para aumentar la fiabilidad de la memoria cuando los datos se cambian a alta frecuencia, la MLC gestionada puede utilizar un modo llamado pSLC (pseudo-Single Level Cell), que emula SLC NAND mediante el almacenamiento de sólo un bit en cada celda MLC. Este enfoque permite que los datos puedan cambiar diez veces más frecuentemente que con el funcionamiento estándar MLC NAND, con niveles comparables de fiabilidad. Esto puede ser útil en aplicaciones tales como decodificadores, que pueden pausar la televisión en vivo, donde los datos se sobrescribe con mucha frecuencia.

El modo pSLC necesita ser activado durante la primera inicialización y el controlador NAND gestiona la memoria MLC como normal.

La última versión del estándar JEDEC, e.MMC v5.0, define una interfaz de mayor velocidad (HS400) para satisfacer las necesidades de los sistemas de alto rendimiento. También incluye un procedimiento de actualización que permite la instalación de una nueva versión del firmware del controlador de dispositivo e.MMC, una vez que el producto está en campo. Una función de notificación del modo SLEEP permite una transición más segura para disminuir los modos de suspensión de energía.

Una característica clave de cualquier versión es la compatibilidad con productos e.MMC que cumplan con las versiones anteriores de la norma. Por esa razón, a la vez que es posible obtener un mejor rendimiento de los nuevos diseños de pines v5.0, el nuevo diseño también es compatible con versiones anteriores.

Tendencias futuras

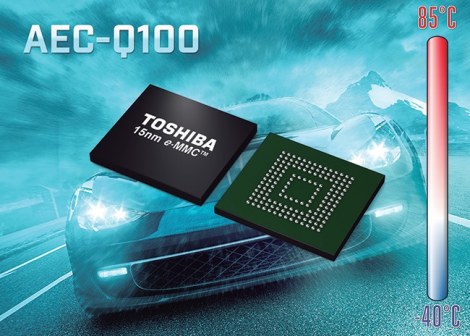

Como con todos los CIs digitales, hay una tendencia hacia un mayor rendimiento y menor consumo de energía en encapsulados más densos; y Toshiba utiliza su nodo de proceso de 15 nm en su flash e.MMC para satisfacer estas necesidades. También hay una necesidad de asegurar que la vida útil de los productos más antiguos se puede ampliar, y BENAND está respondiendo a esas necesidades permitiendo a los ingenieros especificar las últimas tecnologías NAND sin tener que actualizar el hardware del controlador.

También hay tendencia a la ampliación de los rangos de temperatura de funcionamiento para productos flash NAND e.MMC. El rango estándar de temperatura operativa de e.MMC para los productos electrónicos de consumo es de -25 a + 85 ° C. Toshiba ha comenzado a fabricar dispositivos que son adecuados para aplicaciones de información y entretenimiento industriales y de automoción, con un rango de temperatura operativa entre -40 y + 85 °C.

Mirando un poco más allá en el futuro, los súper smartphones de alta gama y tabletas serán los primeros en pasar del actual formato e.MMC. La tecnología ha evolucionado a un nuevo formato llamado almacenamiento flash universal (UFS), que actualmente se encuentra en las primeras etapas de producción en volumen. Con el rendimiento de datos inicial de 300 MB / sg (2,9Gbps por línea) los dispositivos están dirigidos a la parte alta del sector de la electrónica de consumo. Las especificaciones de la próxima generación logran velocidades de línea de 5,8 / 11,6 Gbps y pueden implementarse como soluciones de varias líneas. Los datos pueden ser transferidos a través del bus de serie en ambas direcciones, ascendente y descendente simultáneamente (figura 4).

Los diseñadores de dispositivos inteligentes demandan dispositivos NAND más rápidos, más inteligentes y con mayor capacidad que permiten la compatibilidad con versiones anteriores y una aplicación más fácil. Con amplia experiencia en el desarrollo de sus propias tecnologías, tanto NAND como controladores, Toshiba diseña ambas en conjunto para ofrecer soluciones de memoria fiables y de rendimiento optimizado para dispositivos actuales, futuro e incluso del pasado.