La integración de inteligencia artificial en sistemas embebidos ha dejado de ser una promesa para convertirse en una disciplina de ingeniería con identidad propia. La IA on the Edge no consiste únicamente en ejecutar modelos fuera de la nube; implica rediseñar arquitecturas hardware, optimizar modelos bajo restricciones físicas reales y repensar la relación entre consumo energético, latencia y capacidad de cómputo. El resultado es una nueva generación de dispositivos electrónicos capaces de interpretar su entorno y tomar decisiones de forma autónoma.

Durante años, la arquitectura dominante separó claramente el dispositivo físico del procesamiento inteligente. El sensor capturaba datos; el servidor decidía. Este esquema permitió escalar capacidades de aprendizaje automático aprovechando infraestructuras masivas de cómputo. Sin embargo, cuando la inteligencia se traslada a entornos donde la respuesta debe ser inmediata y determinística, la dependencia de la nube se convierte en un cuello de botella.

En sistemas embebidos críticos, la latencia no puede depender de la congestión de red ni de la disponibilidad de un servicio remoto. Además, la transmisión continua de datos implica consumo energético adicional, incremento del ancho de banda y exposición de información sensible. Estas limitaciones han impulsado un cambio arquitectónico: acercar el procesamiento al origen del dato.

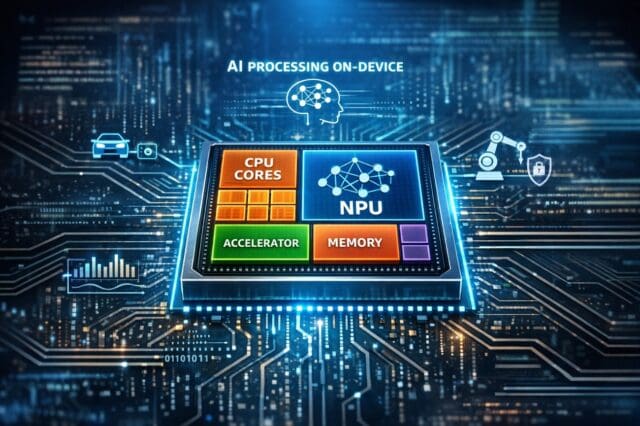

Arquitecturas heterogéneas: CPU, GPU y NPU en el mismo encapsulado

El corazón de la IA on the Edge moderna es la arquitectura heterogénea. Los sistemas en chip actuales combinan núcleos de propósito general con aceleradores específicos diseñados para operaciones tensoriales.

En términos técnicos, las redes neuronales profundas se apoyan en operaciones matriciales masivas, principalmente acumulaciones de productos (MAC). Ejecutar estas operaciones sobre una CPU convencional implica un coste energético elevado y un uso ineficiente de memoria. Las NPUs, en cambio, implementan arrays de procesamiento dedicados, pipelines paralelos y unidades SIMD optimizadas para convoluciones, multiplicaciones matriciales y mecanismos de atención.

A nivel microarquitectural, estos aceleradores incorporan:

- Buffers internos para minimizar accesos a memoria externa.

- Interconexiones de alta velocidad entre unidades MAC.

- Soporte nativo para precisión reducida (INT8, INT4).

- Programadores internos que gestionan el flujo de datos de forma determinística.

La reducción de precisión es clave. Mientras que el entrenamiento suele realizarse en FP32 o FP16, la inferencia puede ejecutarse con enteros de 8 bits o incluso menos, sin degradación significativa de la precisión final. Esta estrategia reduce el ancho de palabra, el consumo dinámico y el tamaño del modelo almacenado en memoria.

El resultado es una mejora sustancial en la relación rendimiento/consumo, métrica determinante en entornos embebidos donde cada miliwatt cuenta.

La memoria como cuello de botella

En sistemas embebidos, la limitación principal no suele ser únicamente la capacidad de cálculo, sino la memoria disponible y el ancho de banda entre bloques funcionales.

Las redes neuronales requieren almacenamiento para:

- Pesos y sesgos.

- Activaciones intermedias.

- Buffers temporales.

- Parámetros de normalización.

En dispositivos con unos pocos cientos de kilobytes de RAM, la gestión de memoria se convierte en un ejercicio de optimización extremo. Las técnicas de reutilización de buffers, la ejecución por capas y la planificación estática del grafo de inferencia son fundamentales.

En plataformas avanzadas, el uso de memorias SRAM internas de alta velocidad permite reducir el acceso a DRAM externa, que es energéticamente más costosa. Algunas arquitecturas emergentes exploran incluso la computación en memoria, donde las operaciones MAC se realizan directamente en matrices de memoria no volátil, reduciendo drásticamente el movimiento de datos, que es una de las principales fuentes de consumo energético.

TinyML: ingeniería bajo restricciones severas

Cuando se desciende al nivel de microcontroladores sin sistema operativo, la integración de IA adquiere un carácter casi artesanal. TinyML obliga a considerar desde el inicio parámetros como:

- Tamaño máximo del modelo en Flash.

- RAM disponible para activaciones.

- Frecuencia de reloj.

- Presupuesto energético por inferencia.

El diseño del modelo no puede separarse del hardware. La elección de la arquitectura —por ejemplo, número de filtros en una CNN o profundidad de una red recurrente— se realiza teniendo en cuenta el consumo estimado de ciclos y memoria.

La cuantización posterior al entrenamiento y la cuantización consciente durante el entrenamiento permiten adaptar los pesos a formatos de menor precisión. Asimismo, el pruning estructural elimina canales completos o filtros redundantes, reduciendo tanto el almacenamiento como la carga computacional.

Este enfoque ha permitido integrar capacidades de mantenimiento predictivo directamente en sensores industriales. Un acelerómetro acoplado a un microcontrolador puede analizar patrones vibracionales y detectar desviaciones respecto a un estado nominal sin necesidad de enviar continuamente datos a la nube.

Del reconocimiento a la comprensión: modelos más complejos en el Edge

La evolución reciente no se limita a modelos pequeños. Plataformas edge de mayor capacidad, como módulos con SoCs multinúcleo y aceleradores dedicados, están comenzando a ejecutar modelos de mayor complejidad.

La optimización de Transformers para entornos edge ha requerido modificaciones sustanciales. El mecanismo de atención, originalmente cuadrático respecto a la longitud de la secuencia, ha sido reemplazado en algunos casos por aproximaciones lineales o por ventanas locales de atención. Además, la compartición de pesos y la destilación desde modelos maestros permiten reducir significativamente el número de parámetros.

En aplicaciones de visión artificial, modelos optimizados pueden realizar detección de objetos en tiempo real con consumo energético contenido. En sistemas multimodales, la combinación de audio, imagen y datos inerciales permite decisiones más robustas sin depender de análisis centralizados.

Toolchains y compiladores específicos

La eficiencia final no depende únicamente del modelo y del hardware, sino del proceso de despliegue. Las herramientas actuales analizan el grafo computacional y lo adaptan a la arquitectura concreta.

Este proceso incluye:

- Fusión de operaciones consecutivas para reducir accesos a memoria.

- Reordenamiento de capas para optimizar el pipeline.

- Asignación estática de buffers.

- Generación de código específico para la NPU.

La optimización es, por tanto, multi-nivel: desde la arquitectura del modelo hasta la generación final de instrucciones máquina.

Seguridad, robustez y ciclo de vida

En aplicaciones industriales y de automoción, la integración de IA debe cumplir requisitos de seguridad funcional. La validación del modelo, la trazabilidad de versiones y la protección frente a modificaciones no autorizadas forman parte del diseño.

Los SoCs modernos incluyen mecanismos de arranque seguro y almacenamiento cifrado que protegen tanto el firmware como los modelos desplegados. Además, la posibilidad de actualización remota segura permite mejorar el modelo a lo largo del ciclo de vida del producto.

La robustez frente a datos adversarios y la gestión de incertidumbre también se convierten en factores relevantes. En sistemas críticos, no basta con obtener una predicción; es necesario estimar su nivel de confianza.

Hacia dispositivos adaptativos

Una línea de investigación creciente es la adaptación local del modelo. Aunque el entrenamiento completo sigue realizándose en infraestructuras de mayor capacidad, algunas técnicas permiten ajustar parámetros finales en función del entorno específico.

Este enfoque resulta especialmente útil en entornos industriales, donde cada máquina puede presentar ligeras variaciones de comportamiento. La capacidad de adaptación incremental mejora la precisión sin necesidad de transmisión masiva de datos.

Una arquitectura distribuida y complementaria

La IA on the Edge no sustituye a la nube; redefine su papel. El entrenamiento masivo, la agregación global de datos y la coordinación de múltiples dispositivos continúan realizándose en infraestructuras centrales. Sin embargo, la inferencia crítica y la decisión inmediata se trasladan al dispositivo.

Se configura así una arquitectura híbrida en la que la inteligencia está distribuida. El sensor ya no es pasivo; el microcontrolador ya no ejecuta únicamente lógica secuencial; el sistema embebido adquiere capacidad de interpretación.

La integración de inteligencia artificial en sistemas embebidos marca un punto de inflexión en el diseño electrónico. La combinación de arquitecturas heterogéneas, técnicas avanzadas de optimización y herramientas de despliegue específicas ha permitido acercar capacidades complejas de inferencia al propio silicio.

En este nuevo escenario, el borde deja de ser un simple extremo de red para convertirse en un nodo inteligente, autónomo y energéticamente eficiente. La electrónica ya no solo mide y transmite: analiza, decide y actúa.

Y esa transformación redefine el papel del ingeniero electrónico en la próxima década.