Autor: Thomas Gleiter, director del segmento del grupo de temporización y comunicación de Microchip Technology

Las redes abiertas de acceso por radio u ORAN (open radio access networks), apoyadas por grupos como TIP (Telecom Infra Project) y la O-RAN Alliance, ofrecen claras ventajas respecto a las antiguas redes cerradas. Sin embargo, es preciso abordar una serie de cuestiones para la adopción exitosa de estas infraestructuras basadas en la desagregación del hardware y el software de la red de acceso por radio mediante interfaces y protocolos de tipo estandarizado y abierto, así como hardware interoperable de varios suministradores. Entre las cuestiones más relevantes está la seguridad de la red que han de tener en cuenta los operadores de redes móviles (ORM) al desplegar infraestructuras ORAN.

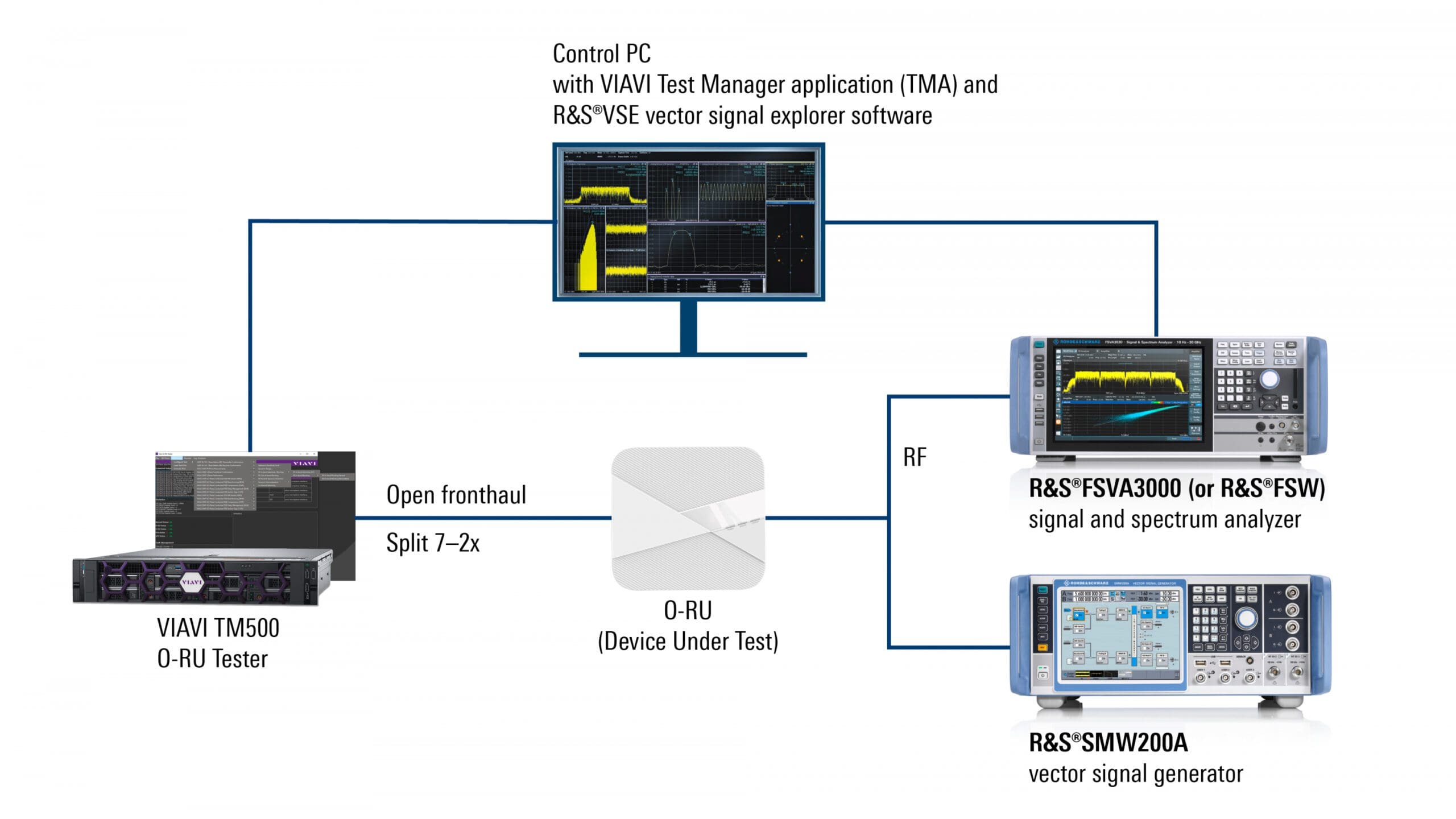

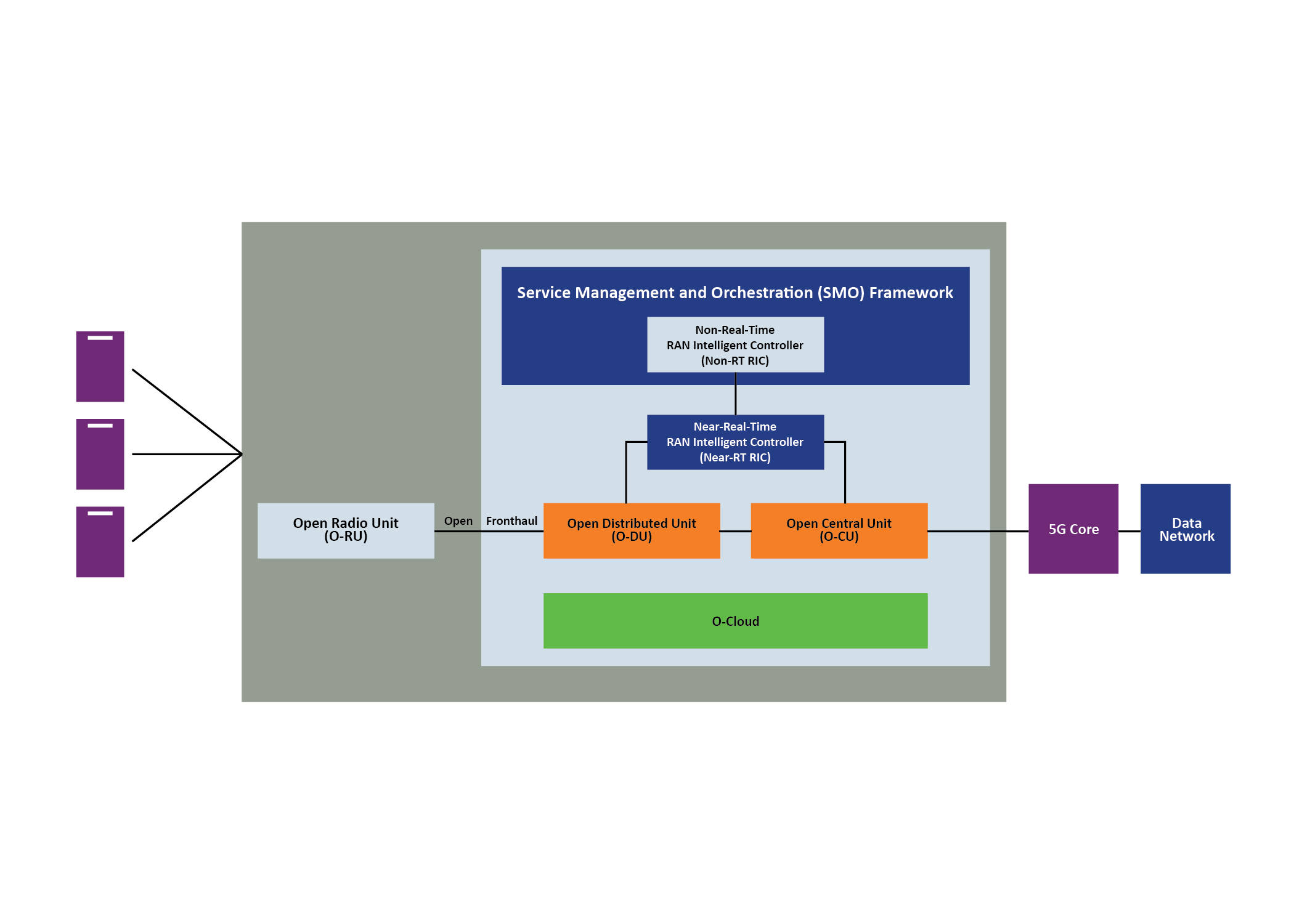

La Figura 1 muestra una arquitectura de red ORAN tal como es definida por la O-RAN Alliance, destacando los principales bloques funcionales de la unidad de radio (RU), la unidad distribuida (DU) y los controladores inteligentes RAN (RIC).

Figura 1: Arquitectura definida por la O-RAN Alliance.

Está previsto que el mercado mundial de ORAN, incluidos el hardware, el software y los servicios, aumente desde 1.100 millones de dólares en 2022 hasta 15.600 millones de dólares en 20271. Este crecimiento se verá protagonizado por los ORM que traten de aprovechar los menores costes de los equipos, el mejor rendimiento de la red y la superior flexibilidad que se obtienen al pasar de sistemas cerrados de tipo propietario a infraestructuras abiertas en ecosistemas con diversos suministradores. Al mismo tiempo, existe una importante voluntad política de impulsar la evolución de ORAN, sobre todo con el anuncio de que el CHIPS and Science Act de 2022 ha asignado 1.500 millones de dólares a financiar el desarrollo de sistemas ORAN.

Desafíos para la seguridad de ORAN

La creación de redes desagregadas con productos de varios suministradores puede hacer que las ORAN sean más vulnerables a los ciberataques que sus homólogas de “sistema cerrado”. Este potencial ha sido especialmente subrayado en EE.UU. por la NSA (National Security Agency) y la CISA (Cybersecurity and Infrastructure Security Agency)1 en su documento titulado “Open Radio Access Network Security Considerations”, que evalúa los aspectos relacionados con la seguridad al implementar una RAN abierta de acuerdo con la arquitectura y las especificaciones de la O-RAN Alliance.

Este documento contempla diversos aspectos técnicos sobre seguridad de ORAN, desde la gestión de varios suministradores y los equipos de radios y estaciones base hasta la inteligencia artificial y cuestiones generales de la red.

El documento indica lo siguiente:

“El despliegue de ORAN añade nuevos elementos de seguridad a los ORM. Por naturaleza, un ecosistema abierto en un entorno con diversos suministradores exige prestar especial atención a la superficie de amenaza en las interfaces entre tecnologías integradas a través de la arquitectura. Además de abordar cuestiones de seguridad relacionadas con la integración de componentes de varios suministradores, los proveedores de servicios tendrán que seguir contemplando otros factores acerca del uso de aplicaciones de código abierto y nuevas funciones e interfaces de redes 5G cuyos estándares aún se hallan en fase de desarrollo. Los ORM también habrán de tener en cuenta cuestiones de seguridad que no son exclusivas de ORAN, como la infraestructura en la nube, la virtualización, contenedorización y el rechazo distribuido de ataques al servicio”.

Uno de los retos cuando se manejan tecnologías de varios suministradores es la asignación de responsabilidades sobre seguridad. En el diseño de redes tradicionales y propietarias, la implementación tendía a recaer bajo la responsabilidad de un solo suministrador, pero con ORAN es posible que los ORM tengan que destinar más tiempo a identificar qué suministradores se han de encargar de la seguridad. También vale la pena destacar que muchos operadores crearán redes ORAN basadas en el núcleo de redes LTE ya existentes, las cuales pueden ser susceptibles a sufrir ataques pasivos por interceptación y ataques activos a través de intermediarios. Además, la superficie de ataque está llamada a ampliarse a medida que crece el número de dispositivos conectados.

El incremento de los gastos de gestión de la seguridad provoca el riesgo de que los costes de la mitigación empiecen a afectar al ahorro de costes que se destaca como una de las principales ventajas de ORAN.

Las posibilidades de virtualización conducen las RAN hacia soluciones basadas en la nube, lo cual significa que los OMR deberían ser capaces de mitigar algunas amenazas sobre la seguridad aprovechando las potentes funciones de seguridad que ya integran las arquitecturas informáticas consolidadas en la nube. No obstante, es posible que muchas redes no puedan ser virtualizadas o que vean su virtualización limitada ya que las ventajas en cuanto a costes (tanto iniciales como el coste total de propiedad) están llamadas a convertirse en el factor más relevante para adoptar las implementaciones que surgirán con el paso del tiempo.

Cómo plantear la seguridad de ORAN

Sea cual sea el grado de virtualización, seguirá habiendo muchos requisitos para la seguridad física a nivel de hardware. Proporcionar esta seguridad conservando las ventajas de ORAN anima a los arquitectos de sistemas a encontrar tecnologías de semiconductores y plataformas de hardware especialmente diseñadas para ofrecer ciberprotección. Entre estas tecnologías se encuentran los procesadores embebidos con funciones de seguridad integradas y “Módulos de Plataforma de Confianza” certificados de acuerdo con especificaciones reconocidas por el sector.

En este sentido tienen especial interés las directrices desarrolladas para a ayudar a fabricantes y suministradores de componentes a implementar una seguridad más potente en sistemas de infraestructuras críticas. Directrices como las incluidas en la Special Publication 800-193 del NIST, que ofrece recomendaciones para aumentar la resiliencia del firmware de la plataforma y los datos frente a ataques potencialmente destructivos.

Las directrices NIST aluden a los componentes de hardware y firmware necesarios para la puesta en marcha y el funcionamiento de un sistema respecto a los ataques que podrían dejar un sistema fuera de servicio de forma temporal o permanente con las consiguientes afectaciones para los usuarios.

Estos son los tres principios básicos de las directrices:

- Proteger: Garantizar que el código y los datos críticos están protegidos frente a cambios, tanto maliciosos como accidentales

- Detectar: Identificar cuándo se han corrompido el código y los datos críticos

- Recuperar: Proporcionar un medio para restaurar el código y los datos críticos a un buen estado conocido

Estos requisitos implican un conjunto de criterios para cualquier sistema seguro que forme parte de la red ORAN:

- Arranque seguro: Uso de una raíz de confianza en el hardware para garantizar la integridad del software durante la puesta en marcha

- Autentificación: Suministro de una identidad única y verificable

- Comunicaciones seguras: Transmisión de datos autentificados y cifrados

- Programación y depuración segura: Control estricto del acceso a las interfaces físicas del sistema. Incluye la eliminación de los puertos de la interfaz utilizados durante el desarrollo del producto pero no necesarios en las unidades de producción

- Protección de activos: Control estricto de contraseñas, claves de cifrado y certificados de seguridad

- Gestión de la vida útil: Evolución de las ciberamenazas en paralelo a la evolución de las medidas de ciberseguridad

- Garantía: Demostración de que todos los dispositivos del sistema son ciberseguros y se han sometido, por ejemplo, a ensayos de penetración

Durante los últimos años, los fabricantes de semiconductores han desarrollado diversas tecnologías que integran funciones y prestaciones para desarrollar equipos que cumplan estos criterios de forma más sencilla y rápida.

Tomemos como ejemplo los controladores embebidos seguros, que fueron diseñados originalmente para aplicaciones informáticas y de almacenamiento en redes pero resultan igual de apropiados para proporcionar seguridad en sistemas abiertos cuyos fabricantes de equipos y arquitectos de sistemas construirán redes ORAN. Estos controladores embebidos incorporan un arranque seguro (raíz de confianza) que combina código inmutable en la ROM de arranque y claves criptográficas públicas/ privadas. Todo el código de la aplicación se debe autentificar con la clave pública antes de la ejecución, mientras que se puede recurrir a un algoritmo de forma digital ECC (Elliptic Curve Cryptography) para autentificar el código y comprobar que no esté corrompido.

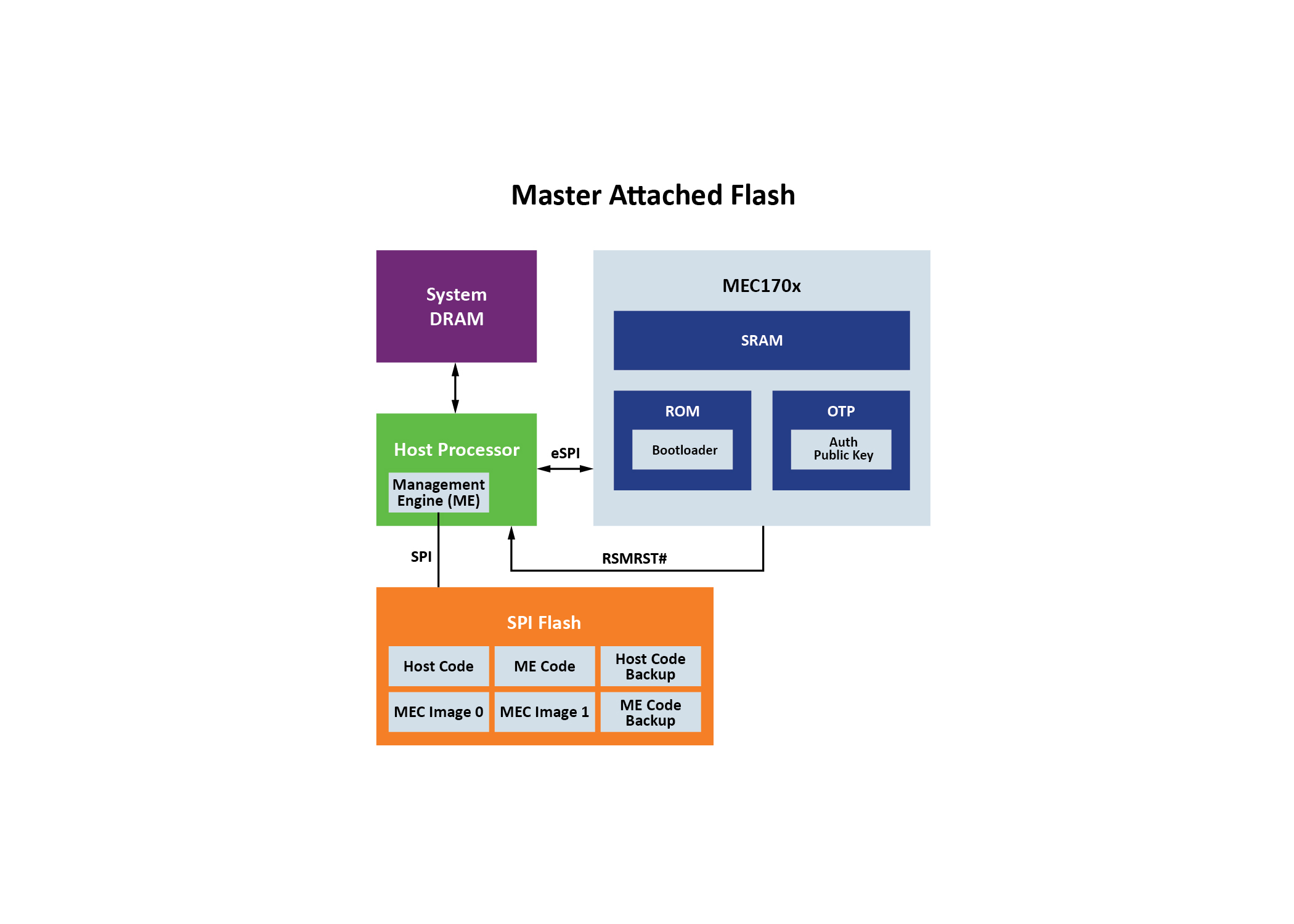

Por lo que respecta a los requisitos de recuperación de NIST, es importante proporcionar redundancia almacenando varias imágenes del código de aplicación de la aplicación en la memoria externa. De esta manera, si en el momento del arranque se detecta que la primera imagen está corrompida, el proceso de arranque se puede realizar con otra imagen. Una vez cargado el código de aplicación, el hardware criptográfico del controlador se puede utilizar para ampliar los requisitos de protección, detección y recuperación al BIOS, el ME (Management Engine) y otro código e información que se almacene en la memoria. En el caso que se detecte código de sistema corrupto, el código de la aplicación puede utilizar imágenes de reserva o “doradas” para restaurar el sistema.

Figura 2: Ejemplo de un controlador embebido seguro con memoria MAF.

La Figura 2 muestra la implementación de un controlador embebido conforme a NIST basado en una configuración de memoria MAF (Master Attached Flash) con un solo chip SPI Flash. Entre las configuraciones alternativas se encuentran MAF con dos chips SPI, Flash compartida con un solo chip SPI y MAF compartida con dos chips SPI.

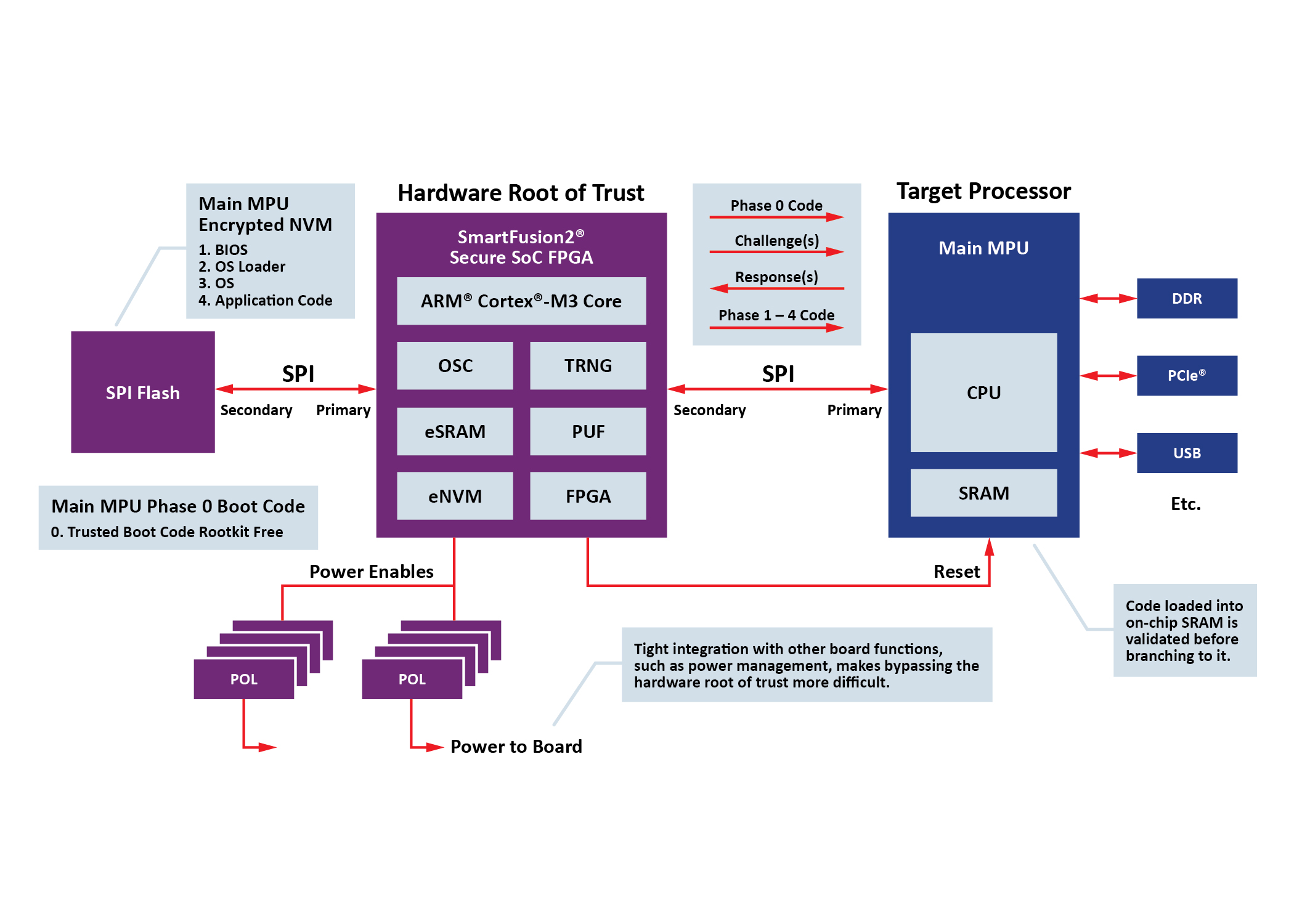

Está claro que el arranque seguro del sistema es un primer paso importante de defensa pero, en algunos casos, las exigencias concretas de la aplicación pueden hacer que los diseñadores de equipos ORAN tengan que basar su hardware en microprocesadores que no ofrecen esta capacidad integrada y, por tanto, no validan código antes de la ejecución. En tales casos será necesario añadir la capacidad de arranque seguro al diseño de los equipos. Una manera de conseguirlo consiste en escoger un diseño de referencia de arranque seguro disponible en el mercado y basado en la tecnología FPGA (field programmable gate array) más avanzada.

Figura 3: Diseño de referencia de arranque seguro basado en FPGA.

Como muestra la Figura 3, estos dispositivos, que utilizan una fuente de confianza y un proceso de autentificación integral, pueden funcionar junto a los procesadores y, en el caso de la solución indicada, incluyen medidas antimanipulación resistentes a DPA (differential power analysis).

Criptoprocesadores autónomos de seguridad

Otra tendencia destacable entre los fabricantes de equipos ORAN es el auge de “criptoprocesadores” especializados y autónomos de seguridad que cumplan las normas FIPS (Federal Information Processing) desarrolladas por el CSRC (Computer Security Resource Center) del NIST y conformes a las especificaciones TCG (Trusted Computing Group).

Las normas FIPS están diseñadas para las agencias federales que utilizan sistemas de seguridad criptográfica con el fin de proteger información sensible en equipos informáticos y de telecomunicaciones, convirtiéndose así en una buena base para introducir seguridad ORAN a nivel de hardware. Los chips conformes a FIPS, que proporcionan un método para almacenar claves hardware protegido y gestionar esas claves para lograr una seguridad multicapa, actúan en la práctica como aceleradores criptográficos de hardware que liberal al procesador principal de las operaciones complejas de seguridad y protegen las claves en el hardware. Dado que estos chips ya han sido muy utilizados en sistemas embebidos, su eficacia ha sido demostrada y se encuentran ampliamente disponibles con un coste económico.

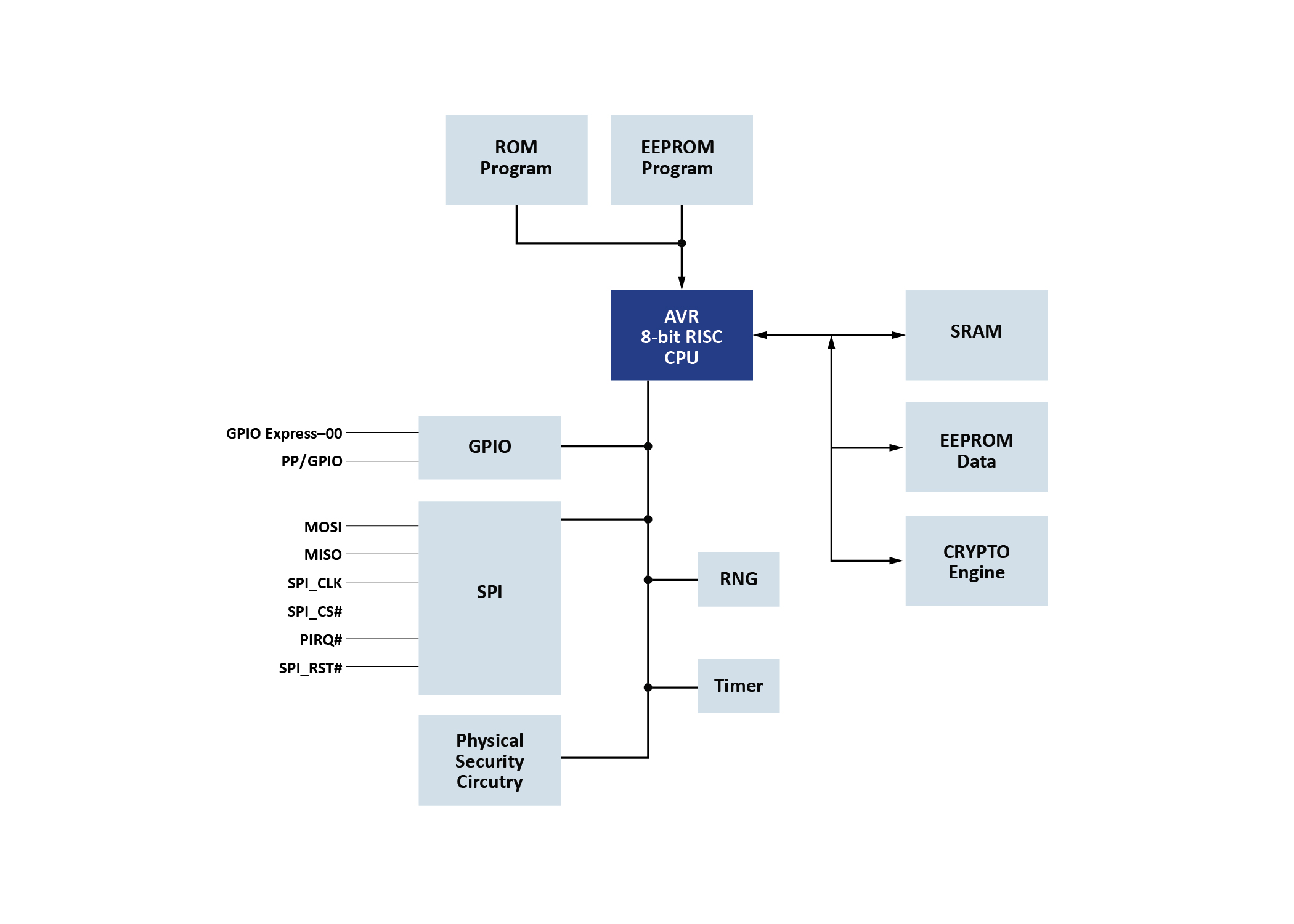

Figura 4: Circuito integrado TPM (Trusted Platform Module) de confianza con interfaz SPI.

La Figura 4 muestra el diagrama de bloques de un criptoprocesadores, formado por un microcontrolador, memoria no volátil protegida y una potente tecnología de seguridad con clave pública (RSA) en un solo chip. El dispositivo aplica la especificación TCG para TPM (trusted platform modules), incorpora un generador de números pseudoaleatorios con certificación FIPS para generación de claves, ofrece arranque seguro, protección de propiedad intelectual, autentificación y comunicaciones seguras e incluye blindaje activo junto con diversas funciones de detección y respuesta frente a intentos de manipulación.

Resumen

La implementación de redes ORAN exige prestar atención a la superficie de amenaza en las interfaces existentes entre las tecnologías integradas en la arquitectura. Además, como muchos operadores crean redes ORAN basadas en el núcleo de redes LTE ya existentes, también pueden ser susceptibles a sufrir ataques pasivos por interceptación y ataques activos a través de intermediarios. Como resultado de ello, los arquitectos de redes deben contemplar la protección y la seguridad de todas las conexiones posibles.

Por definición, las arquitecturas ORAN estarán constituidas en gran parte por tecnologías económicas, disponibles en el mercado y destinadas a una determinada aplicación, que aceleran la implementación y reducen el coste. Y por lo que a la seguridad se refiere, también serán de máxima importancia los semiconductores que ayudan a los diseñadores de hardware a paliar los problemas de seguridad para implementar infraestructuras ORAN robustas y protegidas de próxima generación.

Estos semiconductores deberían cumplir los requisitos de los organismos y las normas correspondientes, como NIST, CISA, FIPS y TCG, proporcionando para ellos funciones que van desde el arranque seguro y la raíz de confianza de hardware hasta generación y autentificación de claves criptográficas, detección frente a intentos de manipulación y soluciones para recuperación del sistema. En un creciente número de casos, tal seguridad se puede encontrar embebidos en controladores y TPM, y donde no está disponible se puede añadir por medio de diseños de referencia probados y listos para usar.