# Referencias de tensión bipolares estabilizadas con FET

J. M. García Barrero, M. P. Dávila Guerrero, M<sup>a</sup> del C. Bermejo Barragán

Escuela de Ingenierías Industriales. Universidad de Extremadura. Badajoz.

*Los circuitos que actúan como referencias de tensión deben proporcionar, una diferencia de potencial a su salida, lo mas constante y estable posible.*

Las causas mas comunes que pueden provocar alteraciones en dicha tensión son:

- Cambios en la tensión de alimentación.

- Variaciones de temperatura.

- Variaciones en la resistencia de carga.

- Interferencias con otros circuitos.

## Figuras de mérito

El comportamiento, frente a esas posibles perturbaciones, se evalúa utilizando figuras de mérito, que cuantifican la sensibilidad de la tensión de referencia, frente los cambios que introducen en las condiciones de trabajo del circuito.

Como figuras de mérito utilizaremos:

- Sensibilidad de la tensión de referencia frente a la de alimentación.

$$S_{V_{CC}}^{V_{REF}} \cong \frac{V_{CC}}{V_{REF}} \cdot \frac{\Delta V_{REF}}{\Delta V_{CC}}$$

- Relación de rechazo de la tensión de alimentación.

$$CT(V_{REF}) = \frac{1}{V_{REF}} \cdot \frac{\Delta V_{REF}}{\Delta T} = \frac{1}{T} \cdot S_T^{V_{REF}}$$

- Coeficiente de temperatura del voltaje de referencia.

$$CT(V_{REF}) = \frac{1}{V_{REF}} \cdot \frac{\Delta V_{REF}}{\Delta T} = \frac{1}{T} \cdot S_T^{V_{REF}}$$

- Regulación de carga.

$$RC = \frac{\Delta V_{REF}}{\Delta I_o}$$

Normalmente estos circuitos se diseñan para suministrar poca potencia de salida.

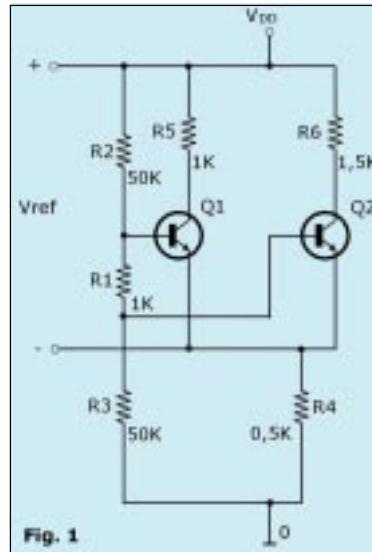

Fig. 1

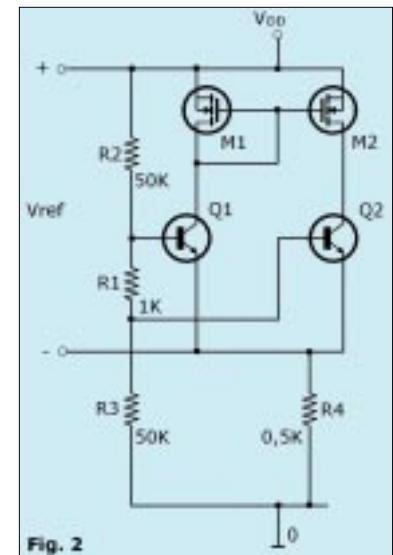

Fig. 2

## Referencias de Banda Prohibida

Se basan en utilizar las caídas Base-Emitor de transistores bipolares o Puerta-Fuente de FET, para obtener tensiones estables.

Partiremos de un circuito bipolar, al que iremos introduciendo modificaciones para mejorar la estabilidad de  $V_{REF}$  hasta conseguir un circuito BIFET, con valores muy optimizados de las figuras de mérito.

En el circuito de la fig. 1, despreciando las corrientes de base, podemos escribir que:

haciendo trabajar los transistores con

$$V_{REF} = V_{BE1} \cdot \left( 1 + \frac{R_2}{R_1} \right) - V_{BE2}$$

distintas corrientes de colector.

En nuestro diseño y para una tensión de referencia de 7,015 V., se han obtenido los siguientes valores para las figuras de mérito.

$$S_{V_{CC}}^{V_{REF}} = 0,927;$$

$$CT = -866 \mu V/\text{°C}$$

$$PSRR = 3,735 \text{ dB};$$

$$RC = 45 \Omega$$

Si polarizamos los colectores de Q1 y Q2 con una carga activa CMOS quedará el circuito de la fig. 2.

Haciendo que los transistores bipolares trabajen con idéntica polarización y para la misma tensión de referencia, obtenemos valores, prácticamente idénticos al del caso anterior.

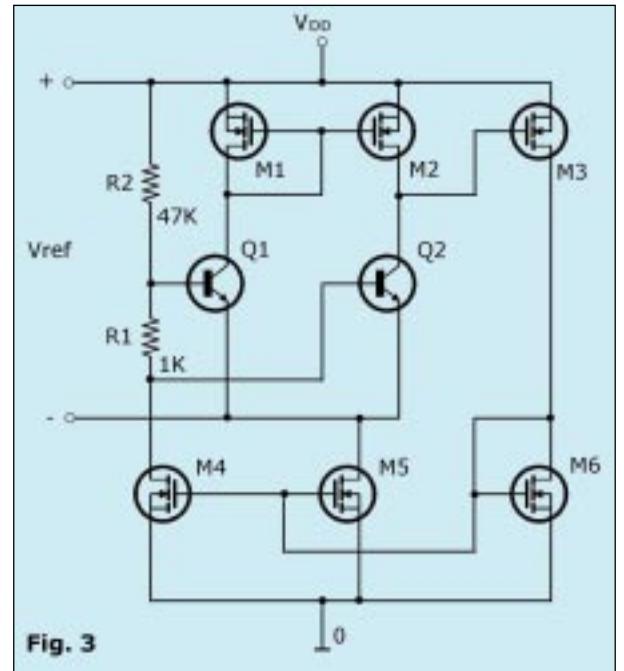

Si sustituimos  $R_3/R_4$  por otra fuente de corriente MOS similar (fig. 3), manteniendo idénticas condiciones de trabajo y dimensionando los transistores de forma adecuada para mantener el valor de  $V_{REF}$ , obtenemos los siguientes valores para las figuras de mérito.

$$S_{V_{CC}}^{V_{REF}} = 1,75 \cdot 10^{-5}$$

$$CT = 1,12 mV/\text{°C}$$

$$PSRR = 59,46 \text{ dB}$$

$$RC = 225,06 \Omega$$

Donde vemos una tensión de salida con una dependencia prácticamente nula de la tensión de alimentación junto a un coeficiente de temperatura muy aceptable, ya que variaciones de temperatura del orden de las producidas en el ambiente, provocarán variaciones de la tensión

de referencia inferiores a 26 mV. Menores que el de su valor a la temperatura nominal.

La relación de rechazo de la tensión de alimentación se ha medido superponiendo a  $V_{DD}$  una tensión senoidal de 0,1V. de amplitud y 1kHz de frecuencia, su valor aumenta de forma considerable respecto al circuito anterior, de acuerdo con el valor obtenido para la sensibilidad de la tensión de referencia frente a  $V_{DD}$ .

La regulación de carga se ha obtenido provocando variaciones de corriente del orden de  $1\mu A$  mediante una fuente de tensión triangular superpuesta a los terminales de salida. El valor obtenido, aunque mayor que el anterior, está dentro de la tolerancia admitida. Por lo que podemos concluir que el circuito de la fig.3 constituye una referencia de tensión muy estable.

## Bibliografía

- "Diseño de Circuitos y Sistemas Integrados." Rubio y otros. Ediciones UPC / Septiembre 2000

- "Referencias de Tensión Específicas. Figuras de Mérito." Mari Paz Dávila Guerrero. Escuela de Ingenierías Industriales. UEX. Badajoz / Junio 2002

- "Analog Integrated Circuits Desing". Johns / Martin Wlley / 1997

- "A precision CMOS Bandgap Ref." IEEE / Journal Of Solid State Circuits Vol 19 / n° 6 / pp 10014-1021.

- "Consideraciones de rendimiento de fuentes de corriente a transistores". María del Carmen Bermejo Barragán. Escuela de Ingenierías Industriales. UEX. Badajoz / Feb. 2001. □

Fig. 3