Una importante parte del desarrollo de dispositivos de almacenamiento es la etapa de prueba de interoperabilidad. El objetivo global es asegurar que el sistema bajo prueba (SUT) cumpla las especificaciones de calidad y diseño a través de un test de alcance total. La selección de las herramientas de prueba adecuadas y poniéndolas frente a las especificaciones de la prueba del sistema, puede, a veces, llevar a una cobertura incompleta de las pruebas a realizar si las limitaciones de las herramientas de test no son bien comprendidas. Esto se aplica especialmente a los recientes interfaces host PCI Express (PCIe) de dispositivos de almacenamiento. Las comunicaciones de datos han realizado un gran salto con esta tecnología, En un esfuerzo por incrementar el rendimiento, las estructuras de los protocolos son más avnazadas. A diferencia de las generaciones anteriores de periféricos de almacenamiento estas nuevas estructuras utilizan mecanismos de codificación de protección de datos para asegurar la fiabilidad de la transmisión. Por ejemplo, las estructuras de comandos de almacenamiento para protocolos tales como Non-Volatile Memory(NVM)Express, SATA Express y SCSI Express, están ahora codificados y contenidas en el payload de PCI Express. Es realmente este cambio el que hace las pruebas más complicadas. Las herramientas de test del pasado ya no sirven para tener el trabajo realizado.

Con los años se han utilizado muchas tecnologías de test por los diseñadores y los ingenieros de pruebas de interoperabilidad para determinar como sus nuevos equipos se van a comportar una vez lanzados al mundo real. Las variaciones en las técnicas de prueba y la selección de las herramientas para cada metodología se basaban en la unicidad de los atributos del protocolo y la fiabilidad del test de realizar la tarea requerida y/o deseada. Un buen ejemplo de esto sería el uso por parte de los ingenieros y técnicos de almacenamiento de “in-line error injectors” para identificar varios temas en tiempo real asociados al protocolo tal como Serial Attached SCSI (SAS).

Los “Inyectores de errores en línea” o “Jammers” tal como son conocidos, son equipos que manipulan o deterioran el tráfico del protocolo en una conexión entre dos nodos o en un link.

Dispositivos de almacenamiento Hosts y Devices (también llamados Initiators y Targets) son un buen ejemplo. Los Jammers crean deliberadamente condiciones de error de forma muy bien controlada por los diseñadores para probar la detección de errores y rutinas de recuperación en los nuevos equipos. Es importante prevenir cambios adicionales de situación o modificación de las características de la transmisión durante la inserción del error, sino los resultados del test serán inciertos.

Un plan de pruebas muy común es realizar una lista de tests describiendo como crear importantes condiciones de error y el criterio que se utilizará para determinar si las respuestas son válidas o no al estímulo del error. Estos escenarios se implementan en el equipo de test y se ejecuta en el sistema bajo prueba (SUT). Tests simples pueden abarcar desde la inserción/supresión de trazas a la sustitución de una respuesta de estado “buena” por una respuesta de estado de “error”. Todo ello se realiza con el objetivo de determinar cuando el sistema reconoced el error y actúa correctamente a la condición creada.

A través de un cuidadoso sistema de test, los mecanismos de recuperación de error han de ser continuamente redefinidos hasta que el dispositivo ofrece un funcionamiento fiable bajo condiciones de operación normales y de estrés. El objetivo global es asegurar que el SUT cumple las especificaciones de diseño y calidad mediante una comprensiva cobertura de pruebas.

Capacidades de Test del Jammer

El Jammer se conecta normalmente cableando directamente enter de Initiator y el Target. Los Jammers ideales son eléctricamente invisibles y no-intrusivos en el SUT. Según el plan de control del tráfico del protocolo e introduciendo condiciones de error específicas se puede probar las respuestas del sistema a varios escenarios de caída de la comunicación.

El beneficio real del jammer es que puede realizar un test de error incluyendo las funciones siguientes:

1. Inyectar errores en una situación del mundo real in-line:.

a. Bit error injection

b. CRC modification

c. Frame modification

d. Primitive modification

e. Link connect or disconnect

f. Out of Band(OOB) and Speed Negotiation Window(SNW) modification

2. Verificar si el SUT se recupera de las condiciones de error sin pérdida o corrupción de datos.

Esta simple metodología de test convierte esta herramienta en indispensable en la comunicación de protocolos utilizada en los sistemas de almacenamiento. En los entornos de pruebas de Parallel ATA, SCSI, Fibre Channel y SAS/SATA requieren este tipo de herramientas para determinar el rendimiento del dispositivo en el sistema y cuan bien responde cuando opera bajo condiciones de bus peores de las ideales.

La razón por la que los jammers eran tan efectivos en las aplicaciones tradicionales de almacenamiento era que dejaban un método de test más simple. Anteriormente, en la industria de los ordenadores, las comunicaciones de almacenamiento entre un host initiator y dispositivos target eran menos complicadas,

Cuando una secuencia de comandos se enviaba desde el host, el target devolvía a byte de código de estado indicando que el comando había sido correcto, hallado un error o el target estaba ocupado sirviendo otras peticiones.

Entonces se pasaba al comando siguiente de la secuencia o retransmitido hasta que el mensaje finalmente tenía éxito. Se utilizaban cables de cinta rígidos para transmitir comunicaciones de datos a baja velocidad y las longitudes estaban restringidas por el ruido de crosstalk de los propios cables. Fue en esta época que el jammer se convirtió en una herramienta estándar en las aplicaciones de test de almacenamiento. El proceso de configurar un escenario de error (jam) no era complicado con los escasos mecanismos de salvaguarda del protocolo para interferir modificando el tráfico en línea.

Probando Protocolos de Almacenamiento en el Pasado.

Como la comunicación de datos evolucionó a transmisiones de protocolos serie, las cosas cambiaron desde el punto de vista de la integridad de datos. Finalmente el almacenamiento adoptó arquitecturas de “punto-a-punto” apartándose de los canales compartidos en un intento de incrementar velocidades y reducir la complejidad de los drivers y el coste. Se utilizaron señales diferenciales, codificaciones 8b/10b y primitivas de alineamiento para reducir cuestiones de ruido en la capa física.

En la estructura de información de la traza de la capa de enlace (FISs) se crearon paquetes conteniendo información o mecanismos de datos payload ofreciendo un nivel superior de control de enlace que el que había en los sistemas de control anteriores de Parallel ATA. Una ves los datos eran procesados en la capa de enlace, la capa de transporte procesa la información FIS y envía la carga de datos (payload) a la capa de comandos para su ejecución Estas estructuras de datos se convierten en el foco de los planes de pruebas de verificación.

Los Jammers eran ideales para probar estas estructuras de datos y se utilizaban extensamente por la industria de almacenamiento. A medida que los interfaces de estos protocolos incrementaron su complejidad y velocidad, muchas de las funciones de los jammers tuvieron que revisarse o se redujo su capacidad de análisis reduciendo su capacidad y efectividad total. En los ultimo años, la industria del almacenamiento ha adoptado interfaces SSd basados en PCI Express tales como NVMe, SATA Express y SCSI Express para cubrir las necesidades de continuo aumento del rendimiento reduciendo latencias del protocolo. Los nuevos protocolos utilizan mecanismos de protección de datos codificados que asegure una transmisión de datos fiable como requieren estos interfaces de altas prestaciones.

PCI Express utiliza los siguientes mecanismos de protección de datos por encima de las prestaciones de la existente capa física tales como señalización diferencial, transmisión de datos codificada y amplio espectro de reloj. Las metodologías de test que se han desarrollado alrededor de PCI Express (PCIe) incluyen analizadores de protocolos y generadores de protocolos para generar estímulos controlados de test tanto para sistemas host como device.

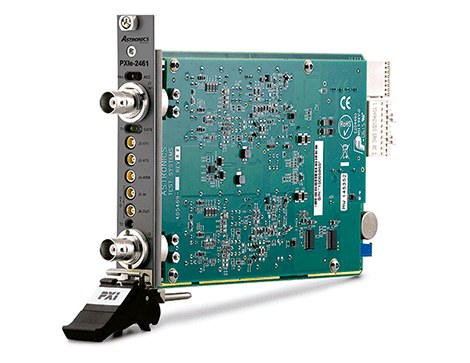

El generador es lo suficientemente flexible como para proveer emulación de bajo nivel de PCIe de host y device. Utilizando el generador se pueden realizar tests de estrés y de casos complejos controlando el tráfico de protocolo incluyendo cambios de la velocidad, ancho de pista, control de flujo, transacciones TLP y DDP. Adicionalmente se pueden crear varias condiciones de error a través de simples técnicas de scripting.

Lógicamente, por parte de la comunidad de validación de almacenamiento ha permanecido el interés en utilizar la metodología y equipamiento previo para validar sistemas de almacenamiento PCIe. Dirigidos por este deseo, se realizaron unos primeros esfuerzos para definir y desarrollar un jammer PCIe. Debido a las limitaciones impuestas por el protocolo PCIe tales como los mecanismos de entrega del protocolo y las estructuras de encapsulado de comando/control, el resultado de estos esfuerzos fue un equipo extremadamente carente en su capacidad de test en general y efectividad al testear sistemas de almacenamiento PCIe, ofreciendo tan solo un pequeño subconjunto de las prestaciones originales que debí realizar. Consecuentemente muchos diseñadores e ingenieros de pruebas de interoperabilidad discontinuaron el uso de jammer y buscaron implementaciones más efectivas.

Accordingly, many designers and interoperability test engineers have discontinued use of the jammer and have moved to more effective test tool implementations. Estas nuevas metodologías están ahora ampliamente extendidas en la industria de servidores, workstation, tarjetas-add-in y sistemas embebidos. Está claro que el protocolo PCI Express tiene en si mismo los mecanismos suficientes para proveer transmisiones de datos punto-a-punto fiables. Las estructuras de comandos y datos de almacenamiento para protocolos tales como NVMe, SATA Express y SCSI Express, están ahora codificados y contenidos en el payload de datos de PCIe. Estos payloads están ahora altamente protegidos en los paquetes (o tramas) de PCIe y son entregados a su destino final sin error.

Debido a estas prestaciones de protección de datos del protocolo PCI Express, estructuras de datos de jamming no son útiles para probar hosts o devices. La lista a continuación inclutye algunas de las limitaciones de los inyectores de error que los desarrolladores habían implementado en los jammers PCIe.

Barreras utilizando Jammers PCIe Jammers en Aplicaciones de Almacenamiento

Hay dos mayores obstáculos que debe superar un jammer para ser una herramienta de pruebas válida para PCIe.

La primera es inyectar sin interrumpir el mecanismo de entrega del protocolo. Si un jammer PCIe se pone entre un device y un host, todos los paquetesde capa física (PHY), enlace y transacción tiene que pasar por el jammer para procesarlo. Al jammer le cuesta tiempo decodificar y procesar cada paquete individualmente para hallar la estructura específica que corromper o modificar. Este retraso afecta los ajustados requerimientos de latencia del ACK que hay en los mecanismos de protección de datos del protocolo PCIe.

Si el jammer añade mucha latencia , cada paquete TLP se reenviará múltiples veces como replay ya que expeira el tiempo de respuesta de retorno del ACK. La constante repetición de TLPs degrada el rendimiento del enlace, desestabiliza la normal transmisión del tráfico e introduce cambios de comportamiento del sistema fuera del alcance de una inserción controlada de errores.

El segundo obstáculo a superar es los comandos de jamming y las estructuras de control. En los protocolos anteriores la cabecera del protocolo contenía información del comando y de control. Durante la transmisión, esta cabecera (que está separada del payload de datos) se leía y entonces posiblemente se manipulaba por el jammer durante la ejecución del preprogramado entorno de error. Los protocolos de almacenamiento PCIe se comportan muy diferentemente con esta información de comando y control, ya que ahora está contenida en el payload (no en la cabecera) del paquete de la capa de transacción (TLP). De hecho, todos los comandos, datos e información de cola están contenidos en el payload de datos. En muchos ámbitos de esta nueva tecnología este es un importante aspecto del protocolo que los desarrolladores quiere testear. Para complicar las cosas, un simple comando puede ahora abarcar un gran número de paquetes TLP. Para un jammer modificar un comando específico de almacenamiento o elemento de datos puede significar tener que capturar un gran número de paquetes TLP. Cada paquete TLP debería ser decodificado, los payloads extraídos ensamblados para crear el comando indicado e identificar correctamente el contenido del elemento destino antes de su modificación. Entonces la secuencia debería ser reensamblada para mantener la estructura del paquete original y redirigirla al link apropiado en ejecución, Adicionalmente el jammer debe mantener una copia del entorno PCIe para entender donde está localizada la dirección base registrada e identificar el punto de inicio de todo el registro de transacciones en el mapa de la memoria para hacer que funcione,

El tiempo necesario para realizar esto por un jammer afecta la latencia global de la transmisión entre el iniciador y el destino. Por estas razones, añadir un jammer en un enlace afecta A continuación vemos un ejemplo de un simple comando ATA dividido entre 48 paquetes TLP separados.

Mejor forma de Test PCIe Storage

Ya que los payloads de datos PCIe están protegidos con sofisticados mecanismos de protección del protocolo, cualquier test realizado con jammer es mejor que vaya dirigido a un subonjunto de la capa de enlace de PCIe. Para obtener un test completo, un exerciser de protocolo PCIe debe ser una parte integral de la configuración del test. La utilización de un exerciser PCIe permite a los usuarios crear un test comprensivo cubriendo comandos y datos de almacenamiento así como un test completo de las capas de enlace y transacción de PCIe.

Un exerciser puede emular un disco host o device en un sistema de almacenamiento. Esto permite al SUT etar fuertemente controlado durante el test sin afectar su rendimiento o los requerimientos de latencia de ACK de un enlace PCIe.

La emulación de un host o device es u na prate importante de la validación y prueba PCIe de las tres últimas generaciones de dispositivos PCIe. Los exercisers ahora soportan las prestaciones de los nuevos interfaces de almacenamiento PCIe, incluyendo administración de colas, registros doorbell y comandos NVMe/SCSI/ATA.

Los drivers de los dispositivos están disponibles permitiendo emulación completa en sistemas para probar el comportamientos de BIOS con consideración del manejo de errores. Los exercisers funcionan mediante métodos de scripts y de control predefinidos. Cada método puede dar rápidamente resultados de test que cubran las necesidades del plan de pruebas.

Para configurar adecuadamentes su sistema de test PCIe es importante seleccionar que herramientas de prueba cubren mejor el área de interés.

El coste es un factor importante en el proceso de selección de los equipos de pruebas para obtener la máxima capacidad de prueba con la inversión realizada. Los laboratorios modernos de test y diseño de soluciones de validación PCIe incorporan analizadores de protocolos y exercisers en sus sistemas para tener la máxima cobertura de pruebas posibles. Los analizadores de protocolos se utilizan para monitorizar el bus mientras múltiples exercisers ofrecen test de interoperabilidad y de estrés. Los jammers PCIe no se consideran válidos debido a su limitada capacidad para realizar test en los SSD de alta velocidad y otros dispositivos de almacenamiento basados en PCIe.