Cómo puede ayudar un generador de forma de onda complementaria integrado en un microcontrolador de 8 bit en aplicaciones de accionamiento de motores

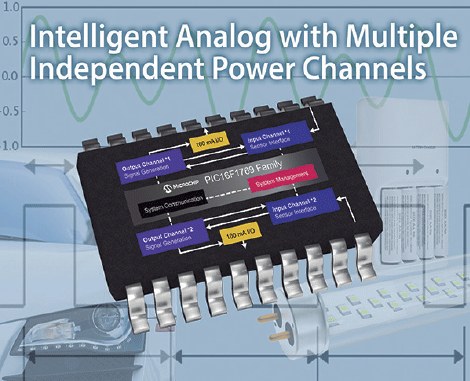

Un generador de forma de onda complementaria (complementary waveform generator, CWG) puede ser práctico cuando se necesita un control mediante medio puente o puente completo, como ocurre por ejemplo en aplicaciones de accionamiento de motores. Aún mejor si el generador también tiene fuentes de entrada seleccionables, control de polaridad, apagado automático y recuperación automática. Algunos microcontroladores de 8 bit ofrecen estas funciones como un periférico, sin cargar el procesador. La Fig. 1 muestra el diagrama de bloques de un periférico de este tipo.

Cada bloque del diagrama representa una función del CWG, que genera una salida complementaria a partir de una de las varias entradas seleccionables.

La salida se puede modificar mediante diferentes modos de funcionamiento, como push-pull, medio puente, puente completo y PWM de mando.

La fuente de reloj se puede seleccionar y utilizar para añadir un retardo de banda muerta entre el par de formas de formas de onda de salida complementarias.

Cada patilla de salida tiene su propio control de activación de salida y la polaridad de estas patillas se puede controlar de manera individual. La salida también se puede interrumpir inmediatamente si se produce un fallo, y recuperarla una vez eliminado el fallo.

Selecciones

Las fuentes de entrada pueden ser entradas externas a la patilla CWGxIN o las salidas procedentes de otros periféricos internos. Los bits de selección de la fuente de entrada se utilizan para seleccionar la fuente de entrada. Los ajustes de selección de las fuentes de entrada y de bit pueden variar de uno a otro dispositivo.

Algunos de los periféricos disponibles que se pueden utilizar como fuentes de entrada son el comparador CCP (capture compare PWM, CCP), el oscilador NCC (numerically controlled oscillator) y la célula lógica configurable CLC (configurable logic cell). En primer lugar, sin embargo, el periférico seleccionado se debería configurar como entrada del CWG.

Para dispositivos que tengan una patilla PPS (peripheral pin select), la patilla de entrada CWGxIN se puede mover a cualquier otra patilla con el registro de selección de entrada de PPS (xxxPPS). Cambiando la notación “xxx” en el nombre del registro a CWGxIN se puede seleccionar cualquier patilla de E/S disponible como CWGxIN.

La salida del CWG se puede modificar para que funcione en cualquiera de los siguientes modos: medio puente; puente completo directo; puente completo inverso; push-pull; y PWM de mando. La selección del modo solo está disponible en algunos dispositivos, en los cuales se puede seleccionar ajustando los bits de selección de modo. Por ejemplo, la Fig. 2 muestra la salida del CWG en diferentes modos de funcionamiento para la familia PIC16F161X de Microchip.

En modo de medio puente se generan dos señales de salida como versiones real e invertida de la entrada. En los modos de puente completo directo e inverso, tres salidas controlan los valores estáticos, mientras que la cuarta salida replica la señal de datos de entrada.

La variación de un bit en los interruptores del registro provoca la conmutación entre el modo directo e inverso.

En modo push-pull, las señales de salida generadas son copias alternas de la entrada. En modo PWM de mando, al activar los bits de mando se puede replicar la señal de eventos de entrada en cualquiera o en las cuatro salidas que tiene el CWG. Cuando se borran los bits de activación de mando, la señal de salida del CWG se determina mediante los bits de datos de mando. Cuando se utiliza un modo de mando síncrono, hace falta que el siguiente evento de entrada tenga lugar antes de que tengan efecto los cambios en los bits de activación de mando.

Por su parte, en modo de mando asíncrono, los cambios en la activación de mando tienen efecto en el siguiente ciclo de instrucción. El reloj de referencia para el control de banda muerta se puede seleccionar a partir de varias fuentes de entrada de reloj diferentes mediante los bits de selección de reloj.

Al igual que ocurre con las fuentes de entrada, las fuentes de reloj disponibles pueden variar entre unos y otros dispositivos.

Control de banda muerta

El control de banda muerta proporciona señales de entrada sin solapamiento durante el modo de medio puente y cambios de dirección durante el modo de puente completo. La señal evita la conducción cruzada de interruptores externos de potencia. La fuente de reloj seleccionada se emplea como referencia para crear un retardo.

Se puede colocar un valor máximo de 6 bit en los registros re recuento de banda muerta de subida y bajada para indicar el número de períodos de retardo del reloj. Cuando CWGxB pasa a nivel bajo, la banda muerta del flanco de subida empieza a contar y retrasa CWGxA durante una décima parte de período antes de pasar a nivel alto. De la misma forma, cuando CWGxA pasa a nivel bajo la banda muerta del flanco de bajada empieza a contar y retrasa CWGxB durante una décima parte de período de reloj antes de pasar a nivel alto.

La banda muerta se sincroniza contando los períodos de reloj a partir de cero y hasta el valor en sus registros de recuento respectivos. Este cálculo de tiempo podría no ser preciso y a ello se le denomina incertidumbre temporal, como indica la Fig. 3.

Cuando las fuentes de subida y bajada que activar el temporizador de banda muerta proceden de entradas asíncronas, como la entrada externa a la patilla CWGxIN, crea una incertidumbre en el tiempo.

Apagado automático

El apagado automático – un funcionamiento activo en modo bajo – se puede activar mediante una fuente de evento de fallo o mediante ejecución de software.

La fuente de evento de fallo se puede seleccionar mediante el registro de control de apagado automático.

Cuando el evento de fallo seleccionado pasa a nivel bajo, la patilla de salida pasará a estado de apagado. El estado de apagado de la patilla de salida se puede seleccionar entre forzado a nivel bajo, forzado a nivel alto, triestado o inactivo, seleccionando para ello los bits de control de estado de apagado automático. El ajuste del bit de apagado del registro de control de apagado automático por software forzará la salida para que pase a estado apagado.

El estado apagado se puede mantener hasta que sea borrado por software automáticamente, lo cual exige permitir el reinicio automático utilizando la patilla de activación de reinicio automático.

Activación de salida

Cada patilla de salida del CWG tiene su propio control de activación. Cuando se borra el bit de activación de una patilla de salida, el CWG no tiene conexión con la patilla de salida. Cuando se activa la salida, se aplica el valor intercalado o la forma de onda activa a la patilla en función de selección de prioridad del puerto interna.

El control de salida se puede anular por completo borrando el bit de activación del módulo. Las activaciones de salida se seleccionan en el CWG mediante los bits de activación de salida. Al ajustar el bit se activa la salida.

Por defecto, el control complementario se configura como inactivo en la salida mientras el control complementario se configura como activo a la salida.

Algunos dispositivos permiten mover la salida del CWG de las patillas por defecto a patillas alternativas mediante la función de patilla alternativa. En los dispositivos que tengan PPS no hay control de salida disponible. En lugar de ello, cada patilla del dispositivo tiene una selección de salida propia y controlada por el registro PPS. Cuando no se seleccionada una entrada en el registro PPS, el periférico no tiene conexión con la patilla de salida.

Control de polaridad

El control de polaridad se pueden aplicar para invertir la señal de salida y la polaridad de cada salida del CWG se puede seleccionar independientemente. Una vez fijado el bit de polaridad de salida, la salida correspondiente pasará a nivel bajo activo. El borrado del bit de polaridad de salida configure la salida correspondiente en nivel alto activo. La inversión de la señal de salida permitiría que dos salidas generaran exactamente la misma señal.

Configuración

Se puede utilizar el configurador de código MPLAB de Microchip para configurar el módulo CWG. Esta herramienta de sencillo manejo se puede conectar al entorno de desarrollo integrado MPLAB X y genera drivers para el control y gobierno de los periféricos de los microcontroladores PIC a partir de los ajustes y selecciones que se hayan realizado en el GUI.

Conclusión

El generador de forma de onda complementaria incorporado en los microcontroladores de 8 bit de Microchip proporciona un control preciso de medio puente y puente completo para las distintas aplicaciones de accionamiento de motores.

Existen fuentes de entrada seleccionables así como control de banda muerta y de polaridad. También puede proporcionar recuperación automática y apagado automático.