## Decisiones difíciles hechas fáciles para mantener la conectividad PCI

Por Rami Sethi

Rami Sethi es director de Marketing de la Enterprise Computing Division en IDT.

Anteriormente, ha ocupado varios cargos de marketing y aplicaciones en IDT, SiTime y Essential Test Systems.

Rami es licenciado en Ingeniería Eléctrica por la Universidad Estatal Politécnica de California, San Luis Obispo.

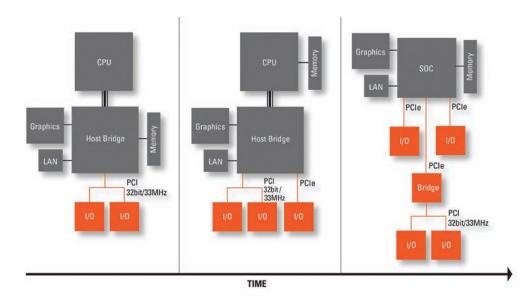

Figura 1. La evolución de los PCI

Durante los últimos seis años, PCI Express® (PCIe®) se ha convertido en la interconexión por excelencia para conjuntos de procesadores, tarjetas adaptadoras, tarjetas E/S y motores gráficos. Las aplicaciones que tradicionalmente dependían de los protocolos heredados para la interconexión de dispositivos, tales como PCI, PCI-X, VME y otros, están adoptando rápidamente nuevas arquitecturas con PCIe.

En particular, PCI, que era ubicuo en aplicaciones desde procesamiento de datos hasta comunicaciones, ha experimentado un declive muy acusado de su soporte en procesadores, conjuntos de chips y circuitos integrados de aplicación específica (véase la figura 1). Desgraciadamente, la transición hacia PCIe no ha sido muy lineal por todos los periféricos que deben conectarse a estos circuitos integrados, como ocurre a menudo en cambios tecnológicos. Por lo tanto, a medida que PCIe va sustituyendo por completo al legado de PCI como interconexión nativa en generaciones sucesivas de microprocesadores, el mantenimiento del soporte de PCI para puntos finales heredados se ha convertido en un problema cada vez más acuciante para los diseñadores de sistemas.

La base instalada de periféricos heredados basados en PCI aún es muy amplia, especialmente en los mercados en los que las plataformas se construven con estructura modular utilizando tarjetas comerciales de distribución general o en los que la hoja de ruta tecnológica tiende a dejar un vacío entre los conjuntos de procesadores y los dispositivos periféricos conectados. Como ejemplos cabe mencionar las placas madre de ordenadores con ranuras de tarjetas adaptadoras PCI para los periféricos o herramientas de depuración heredados, sistemas basados en bastidor con arquitecturas de tarjetas Mezzanine intercambiables, tales como los basados en ATCA (Advanced Telecommunications Computing Architecture), y diseños de placa simple en los que uno o varios puntos finales aún no han adoptado PCle como interfaz nativa.

En las aplicaciones en las que se requiere el soporte de PCI, convendría prestar la debida atención a la hora de seleccionar e implementar la solución de puente adecuada. Las soluciones de puente no suelen ser, por naturaleza, muy elegantes, y el dispositivo de puente apropiado debería ser lo más discreto posible en la aplicación final. Por consiguiente, los principales criterios para la selección de un puente PCIe suelen ser su rendimiento, potencia, coste, espacio de placa y una

compatibilidad eficaz con los últimos estándares y una amplia gama de dispositivos heredados.

Introducir un puente PCIe-PCI donde antes no existía ninguno repercute en el rendimiento, que generalmente se evalúa de nuevo de dos maneras: latencia y caudal. La latencia a través de un puente simplemente puede medirse mediante el tiempo necesario para que una transacción pase por el puente. En el caso de latencia, una cifra baja será más favorable en escenarios de tráfico caracterizados por múltiples transacciones con reducidas cargas útiles de datos. El impacto de la latencia sobre el rendimiento general disminuirá a medida que aumente la carga útil, y el caudal, que se mide en datos que pueden atravesar el puente en un periodo de tiempo determinado, comienza a prevalecer. Respecto al caudal, se pueden distinguir dos tipos de transacción: envíos (escrituras) y retrasos (lecturas). Los límites del caudal global del puente convergen con frecuencia en el rendimiento de las transacciones retrasadas iniciadas desde el dispositivo PCI heredado. Algunas funciones comunes implementadas pueden mejorar el rendimiento del caudal con transacciones retrasadas, como por ejemplo lecturas previas y consultas ascendentes (upstream) concurrentes, iqual que lo pueden hacer funciones más singulares, tales como el almacenamiento en memoria caché a corto plazo. Para maximizar el ancho de banda agregado, una gestión de las transacciones retrasadas del puente proporcionará un máximo de beneficio global.

Puesto que se presta cada vez más atención a la reducción de energía en todo el espectro de aplicaciones, es importante que los puentes PCIe-PCI aprovechen cualquier mecanismo a su alcance para reducir la potencia. Esto incluye una combinación de arquitectura de dispositivos, metodología de diseño e implementación correcta de todos los estados de ahorro de energía definidos en los últimos estándares actualizados. Especialmente

REE • Octubre 2010

relevantes son los diferentes estados de enlace de baja energía definidos en la Especificación de Base del PCIe, que incluye salida rápida y gestión de energía en estado activo, denominada ASPM (Active State Power Management). Las funciones ASPM son muy interesantes en aplicaciones de ordenadores energéticamente eficientes (como los ordenadores con etiquetado Energy Star). Los diseñadores de sistemas que busquen soluciones PCIe de baja energía deberían prestar especial atención a la Especificación de Base del PCIe, particularmente a su revisión de conformidad con un producto determinado. Por ejemplo, aunque ASPM se ha definido en la Revisión 1.0 de la Especificación de Base del PCIe, su implementación en la mayoría de los dispositivos conformes a la Revisión 1.0 no ha sido correcta. Como consecuencia. Microsoft seleccionó la Especificación de Base 1.1 como nivel de soporte requerido a fin de habilitar ASPM para un dispositivo determinado en el sistema operativo.

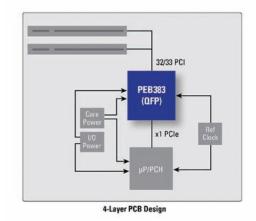

Otro modo muy directo de reducir la energía, además del coste y espacio de placa, consiste en eliminar tantos componentes externos activos como sea posible (véase la figura 2). Los búferes de reloj, generadores de reloj, árbitros de bus y reguladores de tensión son ejemplos claros de dispositivos que permiten tanto una rápida integración como una fácil gestión en chip. Esto va acompañado de algunas consideraciones sobre el soporte para diferentes modos de reloi, número de dispositivos descendentes (downstream) con posibilidad de soporte nativo y nodos de tensión apropiados de la aplicación. Por ejemplo, algunos puentes PCIe utilizan reguladores en chip para reducir las tensiones de alimentación requeridas para el chip. Esto da por resultado menos fuentes de tensión y una reducida necesidad de espacio, pero puede aumentar el consumo de energía en el puente. Alternativamente, los diversos bloques de circuito del puente PCIe se pueden diseñar alrededor de líneas de tensión específicas de modo que se ajusten a las que ya alimentan a otros componentes clave en una aplicación determinada. En las aplicaciones previstas para un dispositivo de este tipo, esto puede reducir enormemente la energía, el coste y la necesidad de espacio de una solución de puente PCIe.

Una de las consideraciones más importantes a la hora de seleccionar un puente PCIe-PCI probablemente es su compatibilidad con todos los dispositivos PCI con los que tendrá que establecer una interfaz in situ. En aplicaciones en las que el puente se conecta con una o más ranuras de PCI, como por ejemplo en placas madre de un ordenador, esta cuestión es especialmente importante porque el fabricante del sistema puede tener enormes dificultades en restringir con qué tipos de periféricos de PCI el usuario puede establecer la conexión. Un buen ejemplo de este problema es la incompatibilidad de muchos puentes PCIe-PCI con tarjetas PCI antiguas que solamente funcionan a una tensión de 5 V. Los puentes que dependen de señales de PCI de 5 V v que no se han diseñado con la debida tolerancia de 5 V sufrirían pérdidas de fiabilidad a largo plazo como consecuencia de la degradación de los búferes de entrada de la interfaz PCI. Otra consideración adquiere relevancia con unos dispositivos periféricos PCI antiguos que tienen direcciones de base fiias que no pueden trasladarse al espacio de direcciones del PCIe y, por lo tanto, no admiten soporte por parte de un dispositivo de puente estándar. El soporte para estos periféricos requiere una función de modo heredado, comúnmente denominada PCI Legacy Mode. Este modo permite decodificación sustractiva en el puerto ascendente de un puente PCIe-PCI, con lo cual las transacciones recibidas que no se decodifican para una dirección interna se reenvían automáticamente a la interfaz PCI y pueden ser reclamadas por los dispositivos en el lado secundario.

Los dos ejemplos anteriores ilustran algunos de los problemas más espinosos

REE • Octubre 2010

## Nuevas arquitecturas con PCle

Figura 2. diseño de placa madre con IDT PEB383 frente a otras soluciones

con la interoperabilidad de puentes PCIe-PCI, pero puede haber otros relacionados con ciertas combinaciones de dispositivos. Antes de tomar en consideración cualquier dispositivo PCIe, siempre conviene consultar la lista de integradores de PCIe, actualizada por el grupo de interés especial PCI-SIG (www.pcisig.com). Este grupo ofrece talleres sobre conformidad en los que las empresas prueban la conformidad con la especificación del PCIe así como la interoperabilidad con otros dispositivos, sistemas y tarjetas de inserción disponibles en la industria. Solamente los dispositivos que han sido aprobados en este proceso riguroso se incluyen en la lista de integradores de PCle, lo cual la convierte en una valiosa referencia para la selección de componentes PCle.

Desde grandes equipos de telecomunicaciones, hechos de hierro, hasta ordenadores personales ultramóviles y puntos de acceso inalámbrico, la eliminación constante del soporte de PCI en los chips de procesamiento central hace que la conectividad con periféricos heredados sea cada vez más difícil sin utilizar las soluciones de puente. Si no se eligen con sumo cuidado, estas soluciones pueden crear muchos quebraderos de cabeza entre los diseñadores de sistemas, desde la desaprobación para el etiquetado de eficiencia energética hasta el colapso de todo el sistema. Afortunadamente, emergen en el mercado nuevas e innovadoras soluciones de puente PCIe, como por ejemplo IDT PEB383, para responder a esta necesidad creciente.